- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10863 > SN75LVDS83BZQLR (Texas Instruments)IC FLATLINK XMITTER 56BGA PDF資料下載

參數(shù)資料

| 型號: | SN75LVDS83BZQLR |

| 廠商: | Texas Instruments |

| 文件頁數(shù): | 27/30頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FLATLINK XMITTER 56BGA |

| 標準包裝: | 1 |

| 系列: | FlatLink™ |

| 類型: | 發(fā)射器 |

| 驅動器/接收器數(shù): | 5/0 |

| 規(guī)程: | LVDS |

| 電源電壓: | 3 V ~ 3.6 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 56-VFBGA |

| 供應商設備封裝: | 56-BGA MICROSTAR JUNIOR(7.0x4.5) |

| 包裝: | 標準包裝 |

| 產(chǎn)品目錄頁面: | 907 (CN2011-ZH PDF) |

| 其它名稱: | 296-24530-6 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當前第27頁第28頁第29頁第30頁

SLLS846B – MAY 2009 – REVISED SEPTEMBER 2011

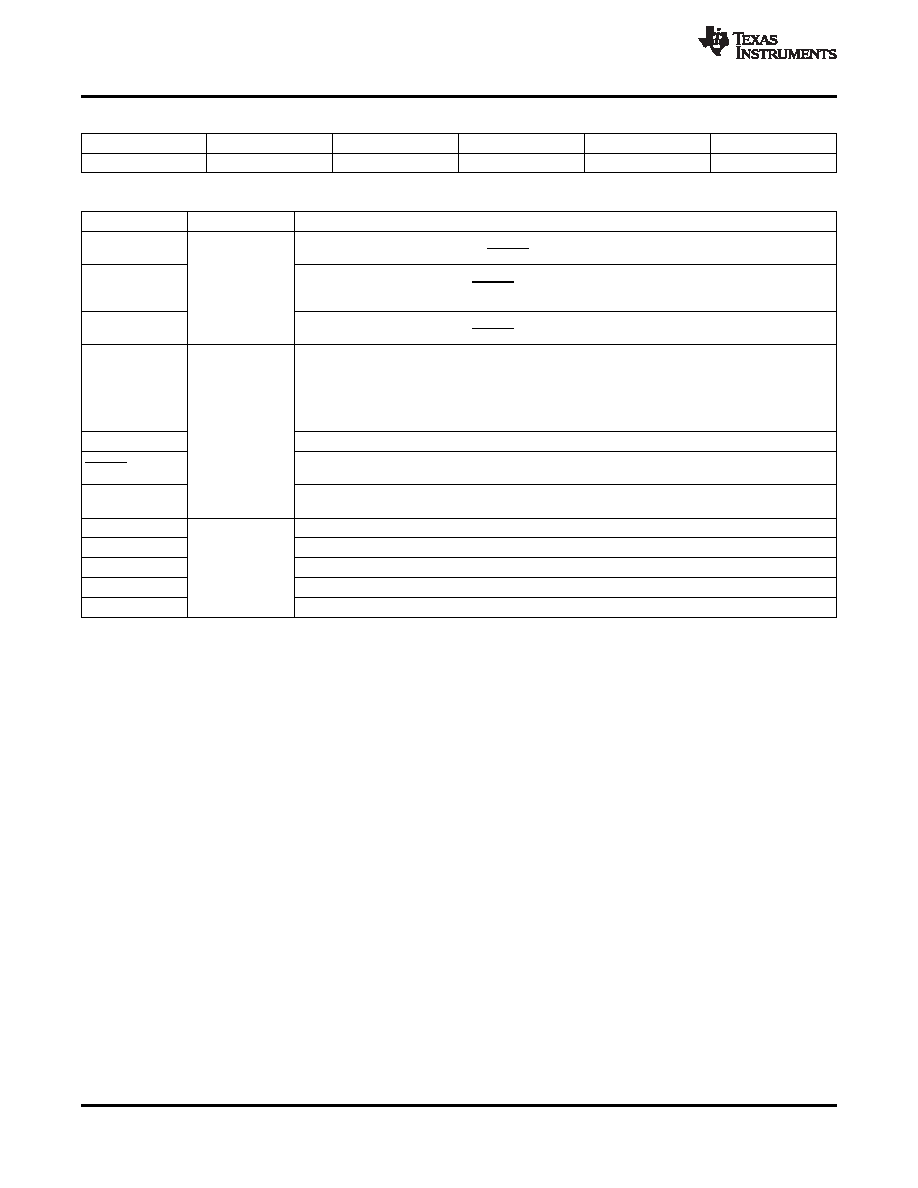

ZQL PIN LIST (continued)

K1

D1

K2

D2

K3

D4

K4

D5

K5

D7

K6

D8

PIN FUNCTIONS

TERMINAL

I/O

DESCRIPTION

Y0P, Y0M, Y1P,

Differential LVDS data outputs.

Y1M, Y2P, Y2M

Outputs are high-impedance when SHTDN is pulled low (de-asserted)

Differential LVDS Data outputs.

Y3P, Y3M

LVDS Out

Output is high-impedance when SHTDN is pulled low (de-asserted).

Note: if the application only requires 18-bit color, this output can be left open.

Differential LVDS pixel clock output.

CLKP, CLKM

Output is high-impedance when SHTDN is pulled low (de-asserted).

Data inputs; supports 1.8V to 3.3V input voltage selectable by VDD supply. To connect a graphic

source successfully to a display, the bit assignment of D[27:0] is critical (and not necessarily

intuitive).

D0 – D27

Note: if application only requires 18-bit color, connect unused inputs D5, D10, D11, D16, D17, D23,

and D27 to GND.

CMOS IN with

pulldn

CLKIN

Input pixel clock; rising or falling clock polarity is selectable by Control input CLKSEL.

Device shut down; pull low (de-assert) to shut down the device (low power, resets all registers) and

SHTDN

high (assert) for normal operation.

Selects between rising edge input clock trigger (CLKSEL = VIH) and falling edge input clock trigger

CLKSEL

(CLKSEL = VIL).

VCC

3.3V digital supply voltage

IOVCC

I/O supply reference voltage (1.8V up to 3.3V matching the GPU data output signal swing)

PLLVCC

Power Supply(1)

3.3V PLL analog supply

LVDSVCC

3.3V LVDS output analog supply

GND

Supply ground for VCC, IOVCC, LVDSVCC, and PLLVCC.

(1)

For a multilayer pcb, it is recommended to keep one common GND layer underneath the device and connect all ground terminals

directly to this plane.

6

Copyright 2009–2011, Texas Instruments Incorporated

相關PDF資料 |

PDF描述 |

|---|---|

| VE-J6K-IX-F3 | CONVERTER MOD DC/DC 40V 75W |

| VE-J6K-IX-F1 | CONVERTER MOD DC/DC 40V 75W |

| VE-J6J-IX-F4 | CONVERTER MOD DC/DC 36V 75W |

| VE-J6J-IX-F3 | CONVERTER MOD DC/DC 36V 75W |

| VE-J6J-IX-F1 | CONVERTER MOD DC/DC 36V 75W |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| SN75LVDS83CZQLR | 功能描述:顯示接口集成電路 FlatLink 10-85MHz Transmitter RoHS:否 制造商:Texas Instruments 電源電流:125 mA 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:WQFN-60 封裝:Reel |

| SN75LVDS83DGG | 功能描述:總線發(fā)射器 Flatlink RoHS:否 制造商:Texas Instruments 數(shù)據(jù)速率:135 Mpps 接口: 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:TSSOP-56 封裝:Reel |

| SN75LVDS83DGG | 制造商:Texas Instruments 功能描述:IC FLATLINK(TM) XMITTER 56-TSSOP 制造商:Texas Instruments 功能描述:IC, FLATLINK(TM) XMITTER 56-TSSOP 制造商:Texas Instruments 功能描述:IC, FLATLINK(TM) XMITTER 56-TSSOP; MSL:MSL 2 - 1 year; SVHC:No SVHC (19-Dec-2012); Base Number:75; Device Type:LVDS; No. of Pins:56; Operating Temperature Max:70C; Operating Temperature Min:0C; Operating Temperature Range:0C to ;RoHS Compliant: Yes |

| SN75LVDS83DGG | 制造商:Texas Instruments 功能描述:SEMICONDUCTOR |

| SN75LVDS83DGGG4 | 功能描述:總線發(fā)射器 Flatlink RoHS:否 制造商:Texas Instruments 數(shù)據(jù)速率:135 Mpps 接口: 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:TSSOP-56 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。