- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373434 > SN74ABT544 (Texas Instruments, Inc.) Octal Registered Transceivers With 3-State Outputs(八記錄收發(fā)器(三態(tài)輸出)) PDF資料下載

參數(shù)資料

| 型號: | SN74ABT544 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Octal Registered Transceivers With 3-State Outputs(八記錄收發(fā)器(三態(tài)輸出)) |

| 中文描述: | 八路注冊收發(fā)器與三態(tài)輸出(八記錄收發(fā)器(三態(tài)輸出)) |

| 文件頁數(shù): | 1/5頁 |

| 文件大小: | 100K |

| 代理商: | SN74ABT544 |

SN54ABT544, SN74ABT544

OCTAL REGISTERED TRANSCEIVERS

WITH 3-STATE OUTPUTS

SCBS189 – FEBRUARY 1991 – REVISED JULY 1993

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

Copyright

1993, Texas Instruments Incorporated

2–1

State-of-the-Art EPIC-

ΙΙ

B

BiCMOS Design

Significantly Reduces Power Dissipation

ESD Protection Exceeds 2000 V Per

MIL-STD-883C, Method 3015; Exceeds

200 V Using Machine Model (C = 200 pF,

R = 0)

Latch-Up Performance Exceeds 500 mA

Per JEDEC Standard JESD-17

Typical V

OLP

(Output Ground Bounce)

< 1 V at V

CC

= 5 V, T

A

= 25

°

C

High-Drive Outputs (–32-mA I

OH

,

64-mA I

OL

)

Package Options Include Plastic

Small-Outline (SOIC) and Shrink

Small-Outline (SSOP) Packages, Ceramic

Chip Carriers, and Plastic and Ceramic

DIPs

description

The

′

ABT544 octal transceiver contains two sets

of D-type latches for temporary storage of data

flowing in either direction. Separate latch-enable

(LEAB or LEBA) and output-enable (OEAB or

OEBA) inputs are provided for each register to

permit independent control in either direction of

data flow.

The A-to-B enable (CEAB) input must be low in

order to enter data from A or to output data from

B. If CEAB is low and LEAB is low, the A-to-B

latches are transparent; a subsequent low-to-high

transition of LEAB puts the A latches in the storage

mode. With CEAB and OEAB both low, the 3-state

B outputs are active and reflect the data present

at the output of the A latches. Data flow from B to

A is similar but requires using the CEBA, LEBA,

and OEBA inputs.

To ensure the high-impedance state during power up or power down, OE should be tied to V

CC

through a pullup

resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

The SN74ABT544 is available in TI’s shrink small-outline package (DB), which provides the same I/O pin count

and functionality of standard small-outline packages in less than half the printed-circuit-board area.

The SN54ABT544 is characterized for operation over the full military temperature range of –55

°

C to 125

°

C. The

SN74ABT544 is characterized for operation from –40

°

C to 85

°

C.

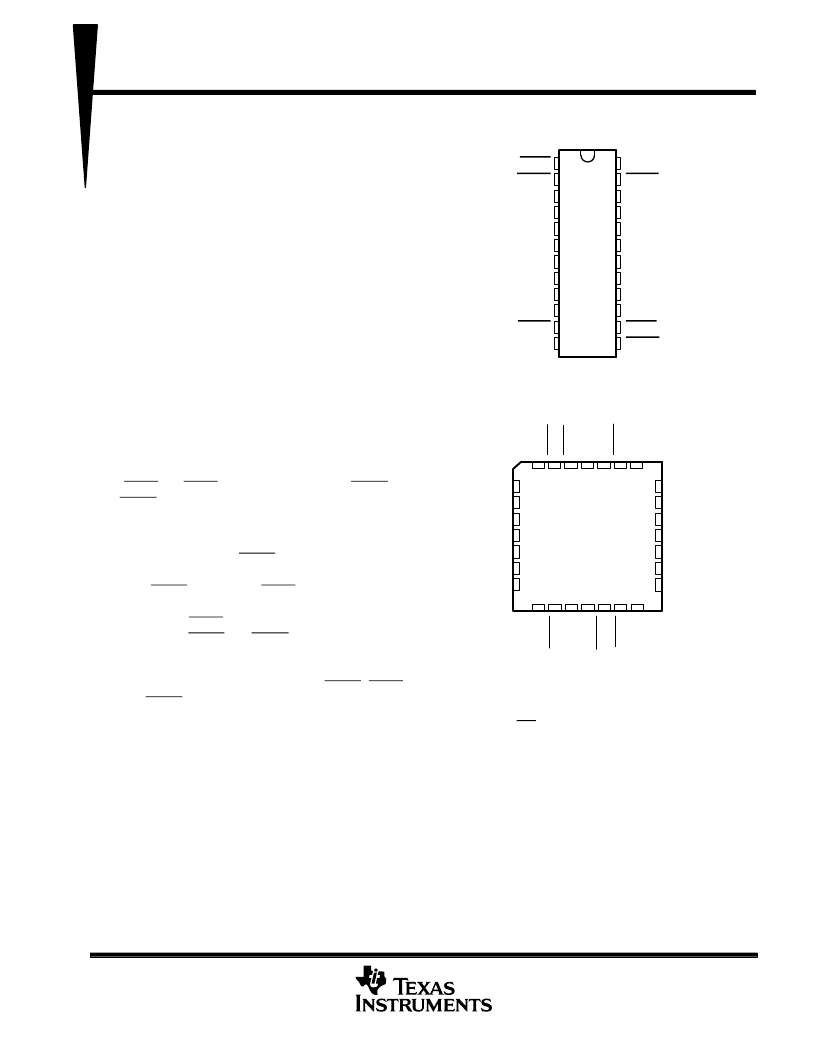

SN54ABT544 . . . JT PACKAGE

SN74ABT544 . . . DB, DW, OR NT PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

LEBA

OEBA

A1

A2

A3

A4

A5

A6

A7

A8

CEAB

GND

V

CC

CEBA

B1

B2

B3

B4

B5

B6

B7

B8

LEAB

OEAB

SN54ABT544 . . . FK PACKAGE

(TOP VIEW)

3 2 1 28 27

12 13

5

6

7

8

9

10

11

25

24

23

22

21

20

19

B2

B3

B4

NC

B5

B6

B7

A2

A3

A4

NC

A5

A6

A7

4

26

14 15 16 1718

A

C

G

N

O

L

B

A

O

L

N

C

B

V

C

NC – No internal connection

EPIC-

ΙΙ

B is a trademark of Texas Instruments Incorporated.

PRODUCT PREVIEW information concerns products in the formative or

design phase of development. Characteristic data and other

specifications are design goals. Texas Instruments reserves the right to

change or discontinue these products without notice.

P

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN54ABT620A | Octal Bus Transceivers With 3-State Outputs(八總線收發(fā)器(三態(tài)輸出)) |

| SN74ABT620A | Octal Bus Transceivers with 3-State Outputs(八總線收發(fā)器(三態(tài)輸出)) |

| SN54ABT623AFK | OCTAL BUS TRANSCEIVERS WITH 3-STATE OUTPUTS |

| SN74ABT623DB | OCTAL BUS TRANSCEIVERS WITH 3-STATE OUTPUTS |

| SN74ABT623NSR | OCTAL BUS TRANSCEIVERS WITH 3-STATE OUTPUTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74ABT573 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:OCTAL TRANSPARENT D-TYPE LATCHES WITH 3-STATE OUTPUTS |

| SN74ABT573A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:OCTAL TRANSPARENT D-TYPE LATCHES WITH 3-STATE OUTPUT |

| SN74ABT573ADB | 制造商:TI 制造商全稱:Texas Instruments 功能描述:OCTAL TRANSPARENT D-TYPE LATCHES WITH 3-STATE OUTPUTS |

| SN74ABT573ADBLE | 制造商:TI 制造商全稱:Texas Instruments 功能描述:OCTAL TRANSPARENT D-TYPE LATCHES WITH 3-STATE OUTPUTS |

| SN74ABT573ADBR | 功能描述:閉鎖 Tri-St Octal D-Type RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。