- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373427 > SMJ4C1024-10HJ (Texas Instruments, Inc.) 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY PDF資料下載

參數(shù)資料

| 型號(hào): | SMJ4C1024-10HJ |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| 中文描述: | 1048576 1位動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器 |

| 文件頁數(shù): | 8/27頁 |

| 文件大?。?/td> | 403K |

| 代理商: | SMJ4C1024-10HJ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

SMJ4C1024

1048576 BY 1-BIT

DYNAMIC RANDOM-ACCESS MEMORY

SGMS023E – DECEMBER 1988 – REVISED MARCH 1996

8

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

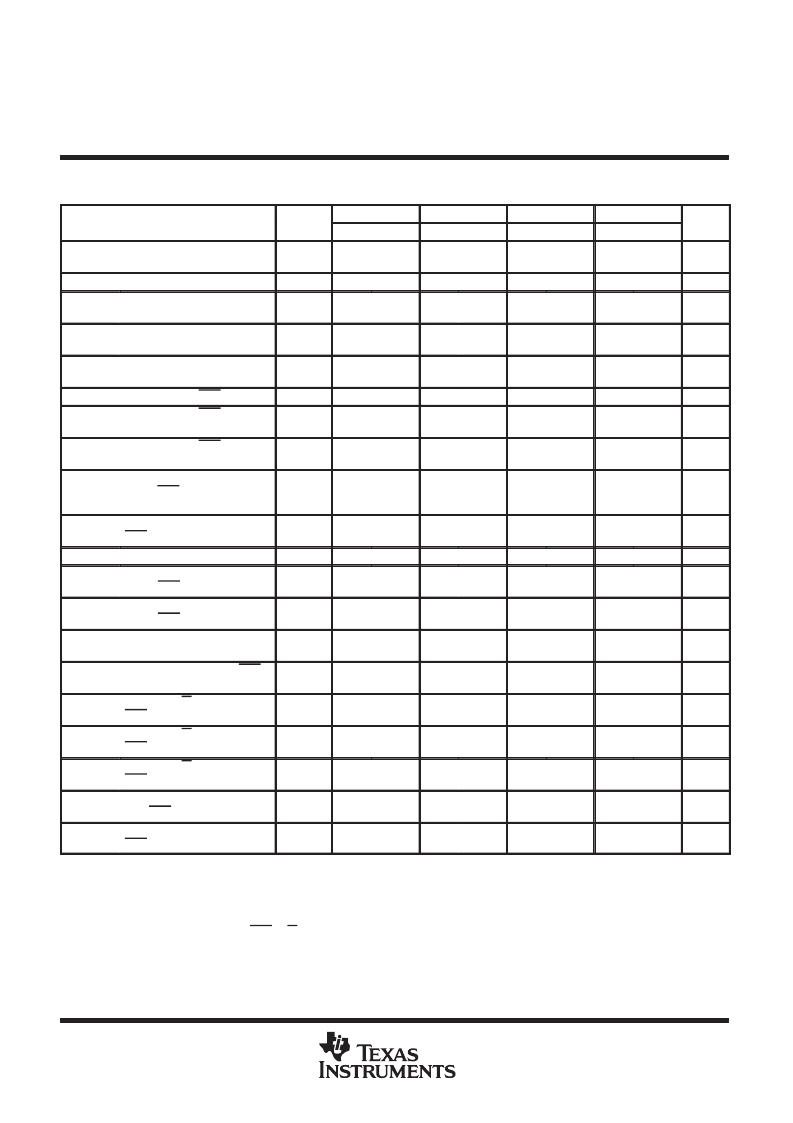

timing requirements over recommended ranges of supply voltage and operating free-air

temperature (see Note 5)

ALT.

’4C1024-80

MIN

’4C1024-10

MIN

’4C1024-12

MIN

’4C1024-15

MIN

UNIT

SYMBOL

MAX

MAX

MAX

MAX

tc(rd)

Cycle time, read

(see Note 6)

tRC

150

190

220

260

ns

tc(W)

Cycle time, write

tWC

150

190

220

260

ns

tc(rdW)

Cycle time,

read-write/read-modify-write

tRWC

175

220

265

315

ns

tc(P)

Cycle time, page-mode read

or write (see Note 7)

tPC

50

55

65

80

ns

tc(PM)

Cycle time, page-mode

read-modify-write

tPRWC

75

85

110

135

ns

tw(CH)

Pulse duration, CAS high

tCP

10

10

15

25

ns

tw(CL)

Pulse duration, CAS low

(see Note 8)

tCAS

20

10000

25

10000

30

10000

40

10000

ns

tw(RH)

Pulse duration, RAS high

(precharge)

tRP

60

80

90

100

ns

tw(RL)

Pulse duration, nonpage

mode, RAS low

(see Note 9)

tRAS

80

10000

100

10000

120

10000

150

10000

ns

tw(RL)P

Pulse duration, page mode,

RAS low (see Note 9)

tRASP

80

100000

100

100000

120

100000

150

100000

ns

tw(WL)

Pulse duration, write

tWP

15

15

20

25

ns

tsu(CA)

Setup time, column address

before CAS low

tASC

0

3

3

3

ns

tsu(RA)

Setup time, row address

before RAS low

tASR

0

0

0

0

ns

tsu(D)

Setup time, data

(see Note 10)

tDS

0

0

0

0

ns

tsu(rd)

Setup time, read before CAS

low

tRCS

0

0

0

0

ns

tsu(WCL)

Setup time, W low before

CAS low (see Note 11)

tWCS

0

0

0

0

ns

tsu(WCH)

Setup time, W low before

CAS high

tCWL

20

25

30

40

ns

tsu(WRH)

Setup time, W low before

RAS high

tRWL

20

25

30

40

ns

th(CA)

Hold time, column address

after CAS low

tCAH

15

20

20

25

ns

th(RA)

Hold time, row address after

RAS low

5. Timing measurements in this table are referenced to VIL max and VIH min.

6. All cycle times assume tt = 5 ns.

7. To assure tc(P) min, tsu(CA) should be

≥

tw(CH).

8. In a read-modify-write cycle, td(CLWL) and tsu(WCH) must be observed.

9. In a read-modify-write cycle, td(RLWL) and tsu(WRH) must be observed.

10. Referenced to the later of CAS or W in write operations

11. Early write operation only

tRAH

12

15

15

20

ns

NOTES:

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SMJ4C1024-10HK | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10HL | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10JD | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10SV | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-12FQ | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SMJ4C1024-10HK | 制造商:TI 制造商全稱:Texas Instruments 功能描述:1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10HL | 制造商:TI 制造商全稱:Texas Instruments 功能描述:1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10JD | 制造商:TI 制造商全稱:Texas Instruments 功能描述:1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10SV | 制造商:TI 制造商全稱:Texas Instruments 功能描述:1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-12FQ | 制造商:TI 制造商全稱:Texas Instruments 功能描述:1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。