- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373427 > SMJ4C1024-10HJ (Texas Instruments, Inc.) 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY PDF資料下載

參數(shù)資料

| 型號(hào): | SMJ4C1024-10HJ |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| 中文描述: | 1048576 1位動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器 |

| 文件頁數(shù): | 4/27頁 |

| 文件大小: | 403K |

| 代理商: | SMJ4C1024-10HJ |

第1頁第2頁第3頁當(dāng)前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

SMJ4C1024

1048576 BY 1-BIT

DYNAMIC RANDOM-ACCESS MEMORY

SGMS023E – DECEMBER 1988 – REVISED MARCH 1996

4

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

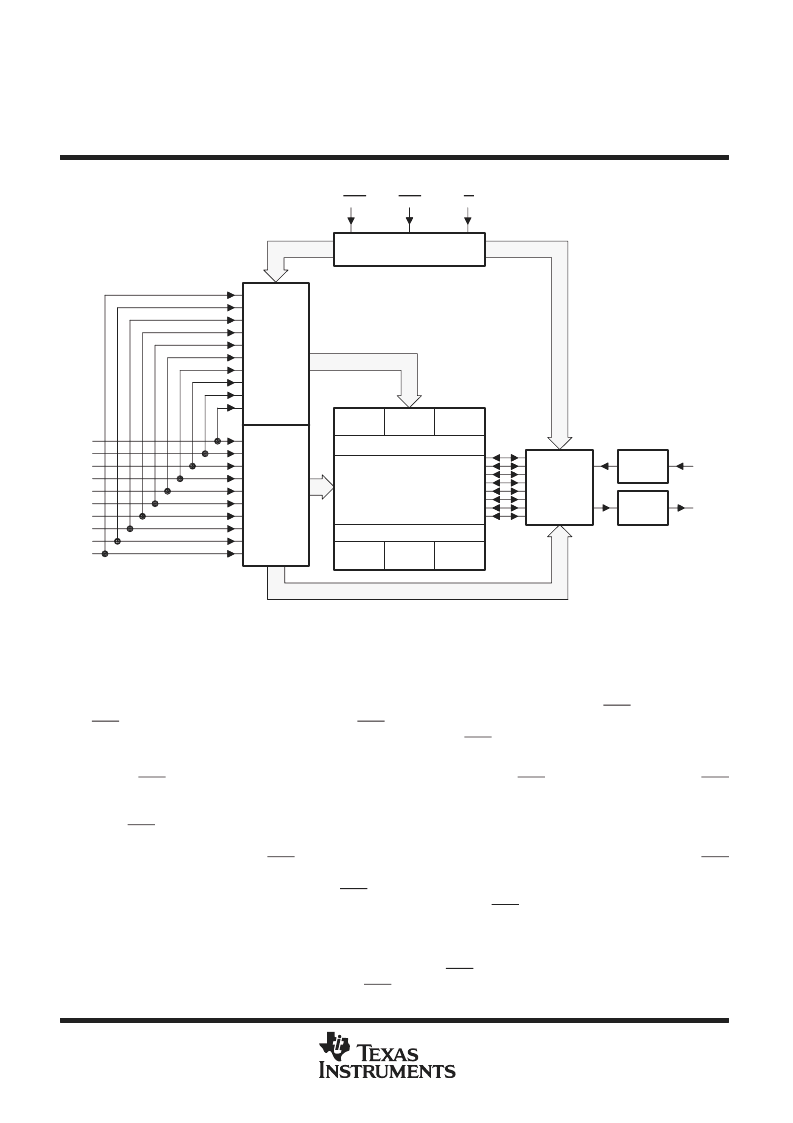

functional block diagram

RAS

CAS

W

Timing and Control

Row

Address

Buffers

(10)

Column

Address

Buffers

(10)

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

256K

Array

Row

Decode

256K

Array

Sense Amplifiers

Sense Amplifiers

256K

Array

Decode

Row

256K

Array

Column Decode

I/O

Buffers

1 of 8

Selection

Data In

Reg.

Data

Out Reg.

D

Q

operation

enhanced page mode

Enhanced page-mode operation allows faster memory access by keeping the same row address while selecting

random column addresses. The time for row-address setup and hold and for address multiplexing is eliminated.

The maximum number of columns that can be accessed is determined by the maximum RAS low time and the

CAS page-cycle time used. With minimum CAS page-cycle time, all 1024 columns specified by column

addresses A0 through A9 can be accessed without intervening RAS cycles.

Unlike conventional page-mode DRAMs, the column-address buffers in this device are activated on the falling

edge of RAS. The buffers act as transparent or flow-through latches while CAS is high. The falling edge of CAS

latches the column addresses. This feature lets the SMJ4C1024 operate at a higher data bandwidth than

conventional page-mode parts, since data retrieval begins as soon as the column address is valid rather than

when CAS goes low. This performance improvement is referred to as enhanced page mode. A valid column

address can be presented immediately after the row-address hold time has been satisfied, usually well in

advance of the falling edge of CAS. In this case, data is obtained after t

a(C)

maximum (access time from CAS

low) if t

a(CA)

maximum (access time from column address) has been satisfied. If the column addresses for the

next page cycle are valid at the same time CAS goes high, access time for the next cycle is determined by the

later occurrence of t

a(CA)

or t

a(CP)

(access time from rising edge of CAS).

address (A0–A9)

Twenty address bits are required to decode one of 1048576 storage cell locations. Ten row-address bits are

set up on inputs A0 through A9 and latched onto the chip by RAS. The ten column-address bits are set up on

pins A0 through A9 and latched onto the chip by CAS. All addresses must be stable on or before the falling edges

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SMJ4C1024-10HK | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10HL | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10JD | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10SV | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-12FQ | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SMJ4C1024-10HK | 制造商:TI 制造商全稱:Texas Instruments 功能描述:1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10HL | 制造商:TI 制造商全稱:Texas Instruments 功能描述:1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10JD | 制造商:TI 制造商全稱:Texas Instruments 功能描述:1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10SV | 制造商:TI 制造商全稱:Texas Instruments 功能描述:1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-12FQ | 制造商:TI 制造商全稱:Texas Instruments 功能描述:1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。