- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373395 > SI4122G (Electronic Theatre Controls, Inc.) DUAL-BAND RF SYNTHESIZER WITH INTEGRATED VCOS FOR GSM AND GPRS WIRELESS COMMUNICATIONS PDF資料下載

參數(shù)資料

| 型號(hào): | SI4122G |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | DUAL-BAND RF SYNTHESIZER WITH INTEGRATED VCOS FOR GSM AND GPRS WIRELESS COMMUNICATIONS |

| 中文描述: | 雙波段射頻合成器集成的GSM和GPRS無線通訊和VCO |

| 文件頁(yè)數(shù): | 8/32頁(yè) |

| 文件大小: | 466K |

| 代理商: | SI4122G |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

Si4133G

8

Rev. 1.1

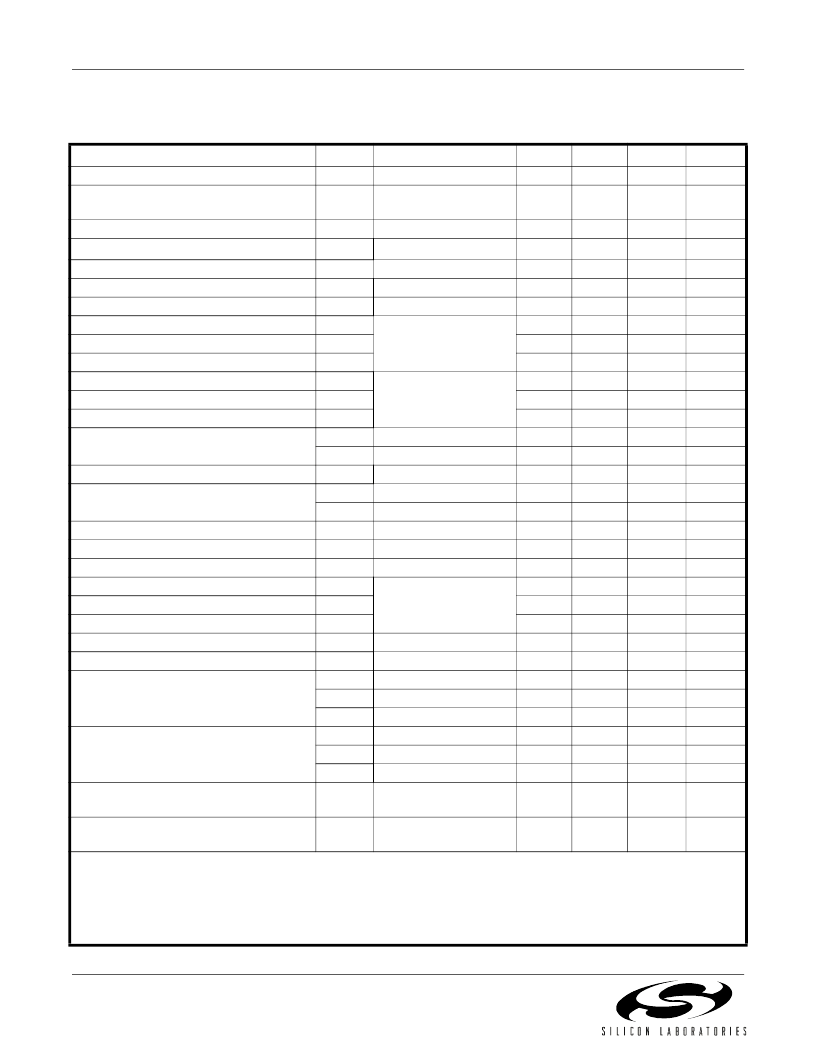

Table 5. RF and IF Synthesizer Characteristics

(V

DD

= 2.7 to 3.6 V, T

A

= –20 to 85°C)

Parameter

1

XIN Input Frequency

Reference Amplifier Sensitivity

Symbol

f

REF

V

REF

Test Condition

Min

—

0.5

Typ

13

—

Max

—

V

DD

+0.3

Unit

MHz

V

PP

Phase Detector Update Frequency

RF1 Center Frequency Range

RF2 Center Frequency Range

IF VCO Center Frequency

Tuning Range from f

CEN

RF1 VCO Pushing

RF2 VCO Pushing

IF VCO Pushing

RF1 VCO Pulling

RF2 VCO Pulling

IF VCO Pulling

RF1 Phase Noise

f

φ

f

φ

= f

REF

/R

200

—

—

—

—

0.5

0.4

0.3

0.4

0.1

0.1

–132

–142

0.9

–134

–144

0.7

–117

0.4

–26

–26

–26

–2

–6

–70

–75

–80

–75

–80

–80

140

KHz

MHz

MHz

MHz

%

MHz/V

MHz/V

MHz/V

MHz

PP

MHz

PP

MHz

PP

dBc/Hz

dBc/Hz

deg rms

dBc/Hz

dBc/Hz

deg rms

dBc/Hz

deg rms

dBc

dBc

dBc

dBm

dBm

dBc

dBc

dBc

dBc

dBc

dBc

μ

s

f

CEN

f

CEN

f

CEN

947

789

526

–5

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

–7

–8

—

—

—

—

—

—

—

1720

1429

952

5

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

1

–1

—

—

—

—

—

—

—

Note: L

EXT

±10%

Open loop

VSWR = 2:1, all

phases, open loop

1 MHz offset

3 MHz offset

100 Hz to 100 kHz

1 MHz offset

3 MHz offset

100 Hz to 100 kHz

100 kHz offset

100 Hz to 100 kHz

Second Harmonic

RF1 Integrated Phase Error

RF2 Phase Noise

RF2 Integrated Phase Error

IF Phase Noise

IF Integrated Phase Error

RF1 Harmonic Suppression

RF2 Harmonic Suppression

IF Harmonic Suppression

RFOUT Power Level

IFOUT Power Level

RF1 Reference Spurs

Z

L

= 50

Z

L

= 50

Offset = 200 kHz

Offset = 400 kHz

Offset = 600 kHz

Offset = 200 kHz

Offset = 400 kHz

Offset = 600 kHz

Figures 4, 5

R

F2 Reference Spurs

Power Up Request to Synthesizer

Ready Time, RF1, RF2, IF

2

Power Down Request to Synthesizer Off

Time

3

Notes:

1.

RF1 = 1.55 GHz, RF2 = 1.2 GHz, IF

=

550 MHz for all parameters unless otherwise noted.

2.

From power up request (PWDNB

↑

or SENB

↑

during a write of 1 to bits PDIB and PDRB in Register 2) to RF and IF

synthesizers ready (settled to within 0.1 ppm frequency error). Typical settling time to 5 degrees phase error is 120

μ

s.

3.

From power down request (PWDNB

↓

, or SENB

↑

during a write of 0 to bits PDIB and PDRB in Register 2) to supply

current equal to I

PWDN

.

t

pup

t

pdn

Figures 4, 5

—

—

100

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Si4123G-BM | DUAL-BAND RF SYNTHESIZER WITH INTEGRATED VCOS FOR GSM AND GPRS WIRELESS COMMUNICATIONS |

| Si4123G-BT* | DUAL-BAND RF SYNTHESIZER WITH INTEGRATED VCOS FOR GSM AND GPRS WIRELESS COMMUNICATIONS |

| Si4133G-BM | DUAL-BAND RF SYNTHESIZER WITH INTEGRATED VCOS FOR GSM AND GPRS WIRELESS COMMUNICATIONS |

| Si4133G-BT* | DUAL-BAND RF SYNTHESIZER WITH INTEGRATED VCOS FOR GSM AND GPRS WIRELESS COMMUNICATIONS |

| Si4123G | DUAL-BAND RF SYNTHESIZER WITH INTEGRATED VCOS FOR GSM AND GPRS WIRELESS COMMUNICATIONS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SI4122G-BM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DUAL-BAND RF SYNTHESIZER WITH INTEGRATED VCOS FOR GSM AND GPRS WIRELESS COMMUNICATIONS |

| SI4122G-BMR | 功能描述:鎖相環(huán) - PLL CONTACT SILICON LABS FOR AVAILABILITY RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| SI4122G-BT | 制造商:SILABS 制造商全稱:SILABS 功能描述:DUAL-BAND RF SYNTHESIZER WITH INTEGRATED VCOS FOR GSM AND GPRS WIRELESS COMMUNICATIONS |

| SI4122GM-EVB | 制造商:Silicon Laboratories Inc 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。