- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄225148 > SC9RS08KA1J3CDB (FREESCALE SEMICONDUCTOR INC) 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PDSO6 PDF資料下載

參數(shù)資料

| 型號(hào): | SC9RS08KA1J3CDB |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PDSO6 |

| 封裝: | 3 X 3 MM, 0.80 MM HEIGHT, ROHS COMPLIANT, DFN-6 |

| 文件頁(yè)數(shù): | 106/134頁(yè) |

| 文件大小: | 3114K |

| 代理商: | SC9RS08KA1J3CDB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)當(dāng)前第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)

Chapter 8 Central Processor Unit (RS08CPUV1)

SC9RS08KA2 Series Data Sheet, Rev. 1

Freescale Semiconductor

73

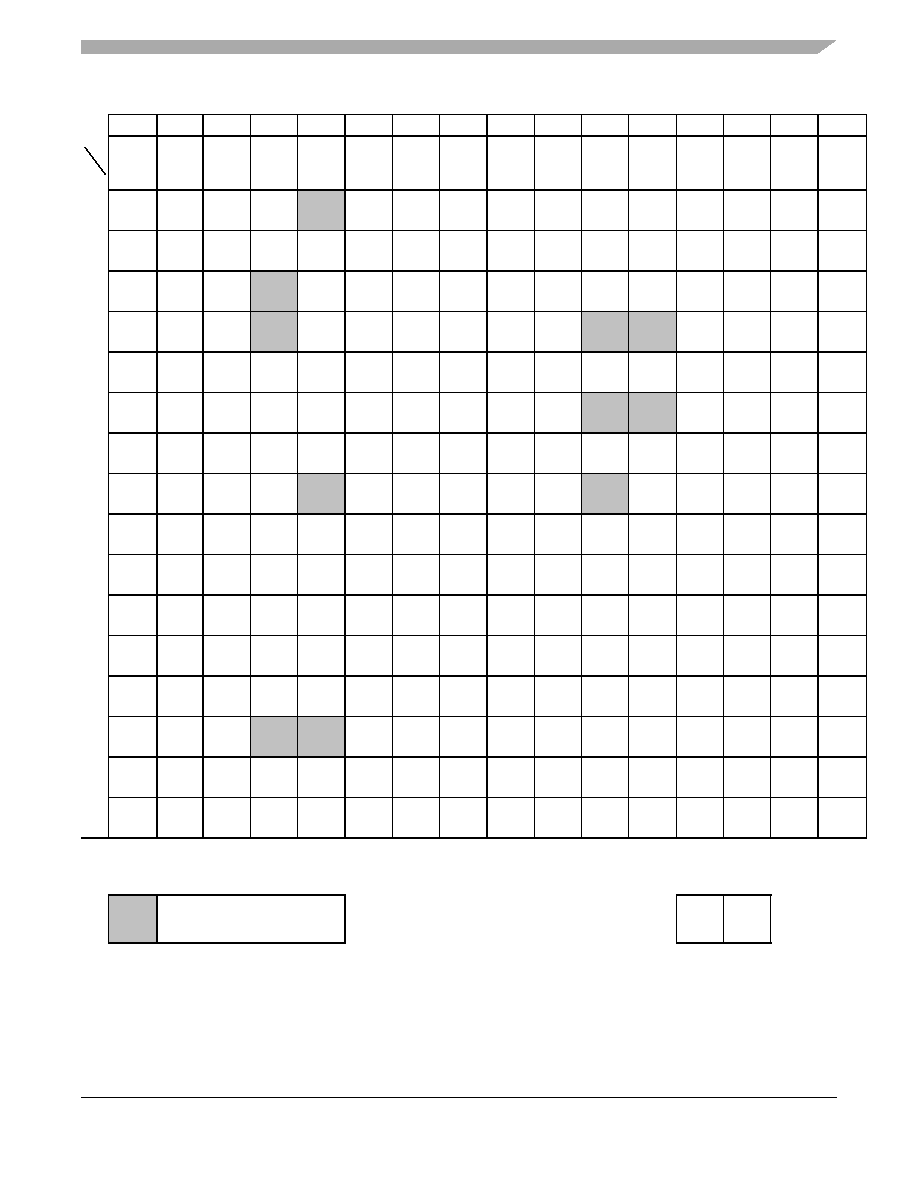

Table 8-2. Opcode Map

DIR

TNY

DIR/REL

INH

TNY

SRT

IMM/INH

DIR/EXT

SRT

0

1

2345

678

9

A

B

C

D

E

F

0

5

BRSET0

3DIR

5

BSET0

2DIR

4

INC

1TNY

3

BRA

2REL

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

2

SUB

2IMM

3

SUB

2DIR

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

1

5

BRCLR0

3DIR

5

BCLR0

2DIR

4

INC

1TNY

5

CBEQ

3DIR

4

CBEQA

3IMM

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

2

CMP

2IMM

3

CMP

2DIR

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

2

5

BRSET1

3DIR

5

BSET1

2DIR

4

INC

1TNY

1

SLA

1INH

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

2

SBC

2IMM

3

SBC

2DIR

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

3

5

BRCLR1

3DIR

5

BCLR1

2DIR

4

INC

1TNY

1

COMA

1INH

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

4

5

BRSET2

3DIR

5

BSET2

2DIR

4

INC

1TNY

3

BCC

2REL

1

LSRA

1INH

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

2

AND

2IMM

3

AND

2DIR

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

5

5

BRCLR2

3DIR

5

BCLR2

2DIR

4

INC

1TNY

3

BCS

2REL

1

SHA

1INH

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

6

5

BRSET3

3DIR

5

BSET3

2DIR

4

INC

1TNY

3

BNE

2REL

1

RORA

1INH

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

2

LDA

2IMM

3

LDA

2DIR

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

7

5

BRCLR3

3DIR

5

BCLR3

2DIR

4

INC

1TNY

3

BEQ

2REL

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

3

STA

2DIR

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

8

5

BRSET4

3DIR

5

BSET4

2DIR

4

INC

1TNY

1

CLC

1INH

1

LSLA

1INH

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

2

EOR

2IMM

3

EOR

2DIR

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

9

5

BRCLR4

3DIR

5

BCLR4

2DIR

4

INC

1TNY

1

SEC

1INH

1

ROLA

1INH

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

2

ADC

2IMM

3

ADC

2DIR

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

A

5

BRSET5

3DIR

5

BSET5

2DIR

4

INC

1TNY

5

DEC

2DIR

1

DECA

1INH

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

2

ORA

2IMM

3

ORA

2DIR

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

B

5

BRCLR5

3DIR

5

BCLR5

2DIR

4

INC

1TNY

6

DBNZ

3DIR

4

DBNZA

2INH

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

2

ADD

2IMM

3

ADD

2DIR

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

C

5

BRSET6

3DIR

5

BSET6

2DIR

4

INC

1TNY

5

INC

2DIR

1

INCA

1INH

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

1

NOP

1INH

4

JMP

3EXT

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

D

5

BRCLR6

3DIR

5

BCLR6

2DIR

4

INC

1TNY

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

3

BSR

2REL

4

JSR

3EXT

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

E

5

BRSET7

3DIR

5

BSET7

2DIR

4

INC

1TNY

4

MOV

3IMD

5

MOV

3DD

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

2+

STOP

1INH

3

RTS

1INH

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

F

5

BRCLR7

3DIR

5

BCLR7

2DIR

4

INC

1TNY

3

CLR

2DIR

1

CLRA

1INH

4

DEC

1TNY

3

ADD

1TNY

3

SUB

1TNY

2

CLR

1SRT

2

CLR

1SRT

2+

WAIT

1INH

5+

BGND

1INH

3

LDA

1SRT

3

LDA

1SRT

2

STA

1SRT

2

STA

1SRT

INH

Inherent

REL

Relative

IMM

Immediate

SRT

Short

DIR

Direct

TNY

Tiny

EXT

Extended

DD

Direct-Direct

IMD

Immediate-Direct

High Byte of Opcode in Hexadecimal

B

Gray box is decoded as illegal instruction

Low Byte of Opcode in Hexadecimal

0

3

SUB

2DIR

RS08 Cycles

Opcode Mnemonic

Number of Bytes /

Addressing Mode

LOW

HIGH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SCA-6 | 0 MHz - 3000 MHz RF/MICROWAVE WIDE BAND LOW POWER AMPLIFIER |

| SCA1N3595US | 0.125 A, 125 V, SILICON, SIGNAL DIODE |

| SCD0705T-6R8M-N | 1 ELEMENT, 6.8 uH, FERRITE-CORE, GENERAL PURPOSE INDUCTOR, SMD |

| SCD0705T-6R8L-N | 1 ELEMENT, 6.8 uH, FERRITE-CORE, GENERAL PURPOSE INDUCTOR, SMD |

| SCD0705T-6R8K-N | 1 ELEMENT, 6.8 uH, FERRITE-CORE, GENERAL PURPOSE INDUCTOR, SMD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SC9RS08KA1J3CPC | 制造商:FREESCALE 制造商全稱(chēng):Freescale Semiconductor, Inc 功能描述:RS08 Microcontrollers |

| SC9RS08KA1J3CSC | 制造商:Freescale Semiconductor 功能描述:8-BIT RS08 CISC 1KB FLASH 2.5V/3.3V/5V 8-PIN SOIC N RAIL - Rail/Tube 制造商:Freescale Semiconductor 功能描述:1K FLASH W/ ACMP 62 RAM |

| SC9RS08KA2 | 制造商:FREESCALE 制造商全稱(chēng):Freescale Semiconductor, Inc 功能描述:RS08 Microcontrollers |

| SC9RS08KA2J3CDB | 制造商:FREESCALE 制造商全稱(chēng):Freescale Semiconductor, Inc 功能描述:RS08 Microcontrollers |

| SC9RS08KA2J3CPC | 制造商:FREESCALE 制造商全稱(chēng):Freescale Semiconductor, Inc 功能描述:RS08 Microcontrollers |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。