- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372115 > SAA7384 (NXP Semiconductors N.V.) Terrestrial digital sound decoder for conventional intercarrier PLL-IF systems PDF資料下載

參數(shù)資料

| 型號: | SAA7384 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Terrestrial digital sound decoder for conventional intercarrier PLL-IF systems |

| 中文描述: | 地面數(shù)字音頻解碼器為傳統(tǒng)載波鎖相環(huán)中頻系統(tǒng) |

| 文件頁數(shù): | 28/40頁 |

| 文件大小: | 182K |

| 代理商: | SAA7384 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

1996 Oct 24

28

Philips Semiconductors

Preliminary specification

Terrestrial digital sound decoder for

conventional intercarrier PLL-IF systems

SAA7284

Notes

1.

It is assumed that all supplies are externally connected at the same source, and consequently that maximum and

minimum values apply simultaneously to each supply.

Cumulative input level based on FM at 0 dB and NICAM at

10 dB with respect to picture carrier.

The signal amplitude present at the SEYE and CEYE pins depends on whether the demodulator is in or out-of-lock.

When out-of-lock, the signal at the pins is

√

2 times the in-lock situation.

VCO jitter is measured in System I over 100 cycles of the VCO clock.

With 10 k

resistor from I

REF

to V

SSF2

.

Audio performance is limited by the dynamic range of the NICAM 728 system. Due to compansion, the quantization

noise is never lower than

62 dB with respect to the input level.

Measured with a

30 dB, 1 kHz NICAM 728 input signal.

Note that a transmitter must internally provide at least a hold time to bridge the undefined region (max. 300 ns) of the

falling edge of SCL.

If a fast I

2

C-bus device is used in an up to 100 kbit/s I

2

C-bus system, then the requirement t

SU;DAT

≥

250 ns is always

fulfilled if this device cannot stretch the LOW level of the SCL signal. If a device stretches the LOW level of the SCL

signal, then data to SDA must be asserted (t

RD(max)

+ t

SU;DAT

) = 1000 + 250 = 1250 ns before the SCL signal is

released to be compatible with the up to 100 kbit/s I

2

C-bus specification.

2.

3.

4.

5.

6.

7.

8.

9.

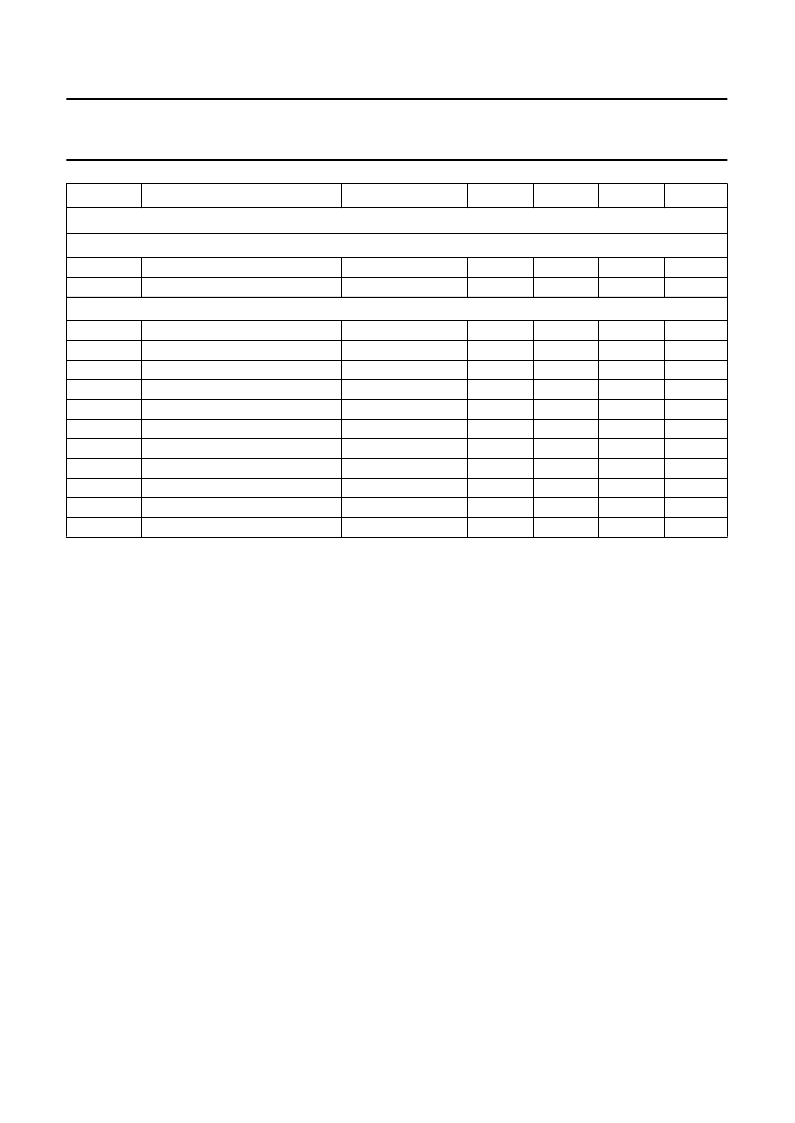

Timing (all timing values refer to V

IH

and V

IL

levels)

DATAIN

WITH RESPECT TO

PCLK (see Fig.9)

t

SU;DAT

t

HD;DAT

SDA

WITH RESPECT TO

SCL(see Fig.10)

data set-up time

data hold time

100

250

ns

ns

f

SCL

t

BUF

t

HD;STA

t

LOW

t

HIGH

t

SU;STA

t

HD;DAT

t

SU;DAT

t

r

t

f

t

SU;STO

SCL clock frequency

bus free time

START code hold time

SCL clock LOW time

SCL clock HIGH time

START code set-up time

data hold time

data set-up time

SDA and SCL rise time

SDA and SCL fall time

STOP code set-up time

0

1300

600

1300

600

600

0

100

50

50

600

400

300

300

kHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

note 8

note 9

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7284 | Terrestrial digital sound decoder for conventional intercarrier PLL-IF systems |

| SAA7284ZP | Terrestrial digital sound decoder for conventional intercarrier PLL-IF systems |

| SAA7324 | Digital servo processor and Compact Disc decoder with integrated DAC (CD10 II)(具有綜合數(shù)模轉(zhuǎn)換器(DAC)的數(shù)字伺服處理器和光盤譯碼器) |

| SAA7325H | Digital servo processor and Compact Disc decoder with integrated DAC CD10 |

| SAA7326H | CABLE ASSEMBLY; TNC MALE TO TNC MALE; 75 OHM, RG59B/U COAX; 12" CABLE LENGTH; *USES STANDARD 50 OHM INTERFACE CONNECTORS* |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7385 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Error correction and host interface IC for CD-ROM SEQUOIA |

| SAA7385GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Error correction and host interface IC for CD-ROM SEQUOIA |

| SAA7388 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Error correction and host interface IC for CD-ROM ELM |

| SAA7388GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Error correction and host interface IC for CD-ROM ELM |

| SAA7390 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:High performance Compact Disc-Recordable CD-R controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。