- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378162 > RM5261-250-Q (PMC-SIERRA INC) RM5261⑩ Microprocessor with 64-Bit System Bus Data Sheet Released PDF資料下載

參數(shù)資料

| 型號: | RM5261-250-Q |

| 廠商: | PMC-SIERRA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | RM5261⑩ Microprocessor with 64-Bit System Bus Data Sheet Released |

| 中文描述: | 64-BIT, 250 MHz, MICROPROCESSOR, PQFP208 |

| 封裝: | POWER, QFP-208 |

| 文件頁數(shù): | 21/40頁 |

| 文件大小: | 683K |

| 代理商: | RM5261-250-Q |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer

’

s Internal Use

Document ID: PMC-2002241, Issue 1

21

RM5261

Microprocessor with 64-Bit System Bus Data Sheet

Released

3.20 Write buffer

Writes to external memory, whether cache miss write-backs or stores to uncached or write-through

addresses, use the on-chip write buffer. The write buffer holds up to four 64-bit address and data

pairs. The entire buffer is used for a data cache write-back and allows the processor to proceed in

parallel with the memory update. For uncached and write-through stores, the write buffer

significantly increases performance by decoupling the

SysAD

bus transfers from the instruction

execution stream.

3.21 System Interface

The system interface consists of a 64-bit Address/Data bus with 8 parity check bits and a 9-bit

command bus. In addition, there are 6 handshake signals and 6 interrupt inputs. The interface is

capable of transferring data between the processor and memory at a peak rate of 800 MB/sec with

a 100 MHz SysClock.

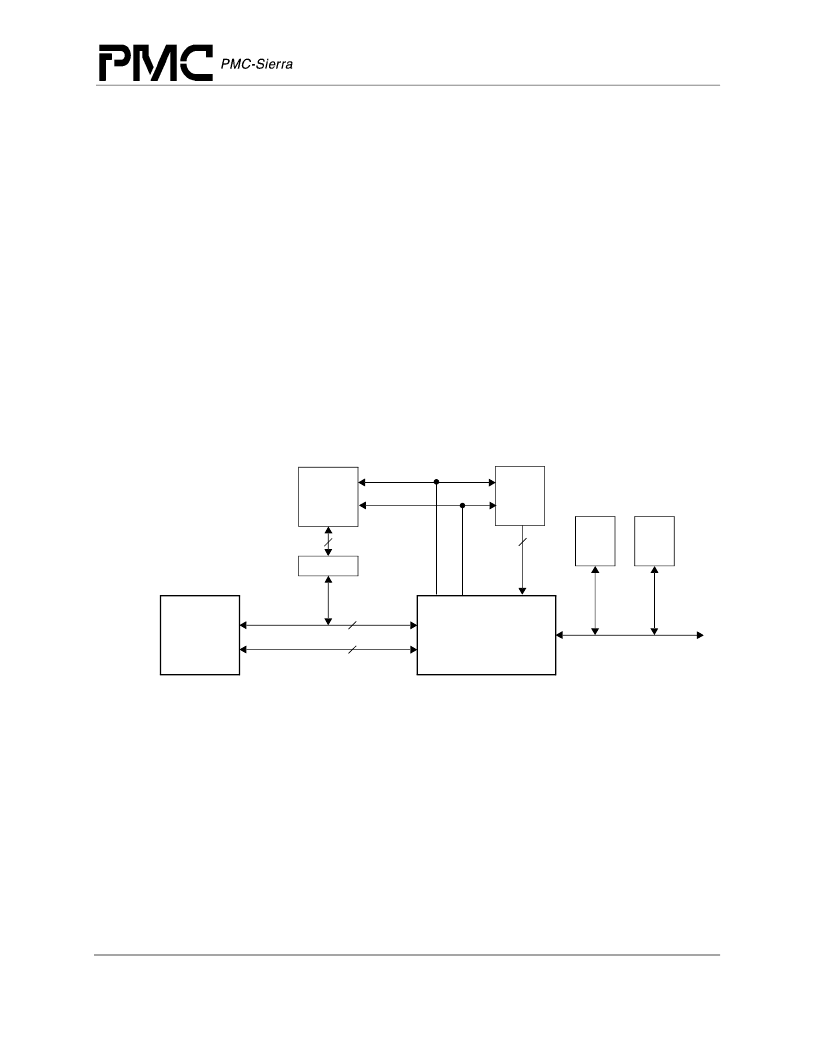

Figure 6 shows a typical embedded system using the RM5261. In this example, a bank of DRAMs

and a memory controller ASIC share the processor

’

s

SysAD

bus while the memory controller

provides separate ports to a boot ROM and an I/O system.

Figure 6 Typical Embedded System Block Diagram

3.22 System Address/Data Bus

The 64-bit System Address Data (

SysAD

) bus is used to transfer addresses and data between the

RM5261 and the rest of the system. It is protected with an 8-bit parity check bus (

SysADC

). The

system interface is configurable to allow easy interfacing to memory and I/O systems of varying

frequencies.

The Block Write data rate, Non-block Write protocol, and Output Drive Strength are

programmable at Boot time via the

Mode Control

bits. The rate at which the processor receives

data is fully controlled by the external device.

3.23 System Command Bus

The RM5261 interface has a 9-bit System Command (

SysCmd

) bus. The command bus indicates

whether the

SysAD

bus carries address or data information on a per-clock basis. If the

SysAD

RM5261

Memory I/O

Controller

Flash/

Boot

Rom

x

x

72

PCI Bus

72

8

23

Latch

DRAM

Control

Address

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RM5261-266-Q | RM5261⑩ Microprocessor with 64-Bit System Bus Data Sheet Released |

| RM7065 | RM7065A⑩ Microprocessor with On-Chip Secondary Cache Data Sheet Preliminary |

| RM7065A | 64-Bit MIPS RISC Microprocessor with Integrated L2 Cache |

| RM7065A-300T | RM7065A⑩ Microprocessor with On-Chip Secondary Cache Data Sheet Preliminary |

| RM7065A-350T | RM7065A⑩ Microprocessor with On-Chip Secondary Cache Data Sheet Preliminary |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RM5261-250Q-C001 | 制造商:PMC Sierra from Components Direct 功能描述:RM5261-250Q-C001, MICROPROCESSOR 64-BIT 0.25 UM CMOS TECHNOL - Trays 制造商:PMC-Sierra 功能描述:PMC SIERRA RM5261-250Q-C001, Microprocessor 64-Bit 0.25 um CMOS Technology 3.3V 208-Pin PQFP |

| RM5261-266Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM5261A | 制造商:PMC 制造商全稱:PMC 功能描述:64-Bit MIPS RISC Microprocessor with 32/64-Bit System Bus |

| RM5261A-300HI-B002 | 制造商:PMC Sierra from Components Direct 功能描述:MICROPROCESSOR 64-BIT 300MHZ 0.18UM TECHNOLOGY - Trays 制造商:PMC-Sierra 功能描述:PMC SIERRA RM5261A-300HI-B002, Microprocessor 64-Bit 300MHz 0.18um Technology 3.3V 208-Pin MQFP |

| RM5261A-300J-B002 | 制造商:PMC Sierra from Components Direct 功能描述:RM5261A-300J-B002, MICROPROCESSOR 64-BIT 300MHZ 0.18UM TECHN - Trays 制造商:PMC SIERRA 功能描述:PMC SIERRA RM5261A-300J-B002, Microprocessor 64-Bit 300MHz 0.18um Technology 3.3V 208-Pin LFMQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復。