- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄296941 > QL6250E-7PQ208M (QUICKLOGIC CORP) FPGA, 960 CLBS, 248160 GATES, PQFP208 PDF資料下載

參數(shù)資料

| 型號(hào): | QL6250E-7PQ208M |

| 廠(chǎng)商: | QUICKLOGIC CORP |

| 元件分類(lèi): | FPGA |

| 英文描述: | FPGA, 960 CLBS, 248160 GATES, PQFP208 |

| 封裝: | 28 X 28 MM, 3.35 MM HEIGHT, MS-028, PLASTIC, QFP-208 |

| 文件頁(yè)數(shù): | 20/64頁(yè) |

| 文件大?。?/td> | 850K |

| 代理商: | QL6250E-7PQ208M |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

2006 QuickLogic Corporation

Eclipse-E Family Data Sheet Rev. A

27

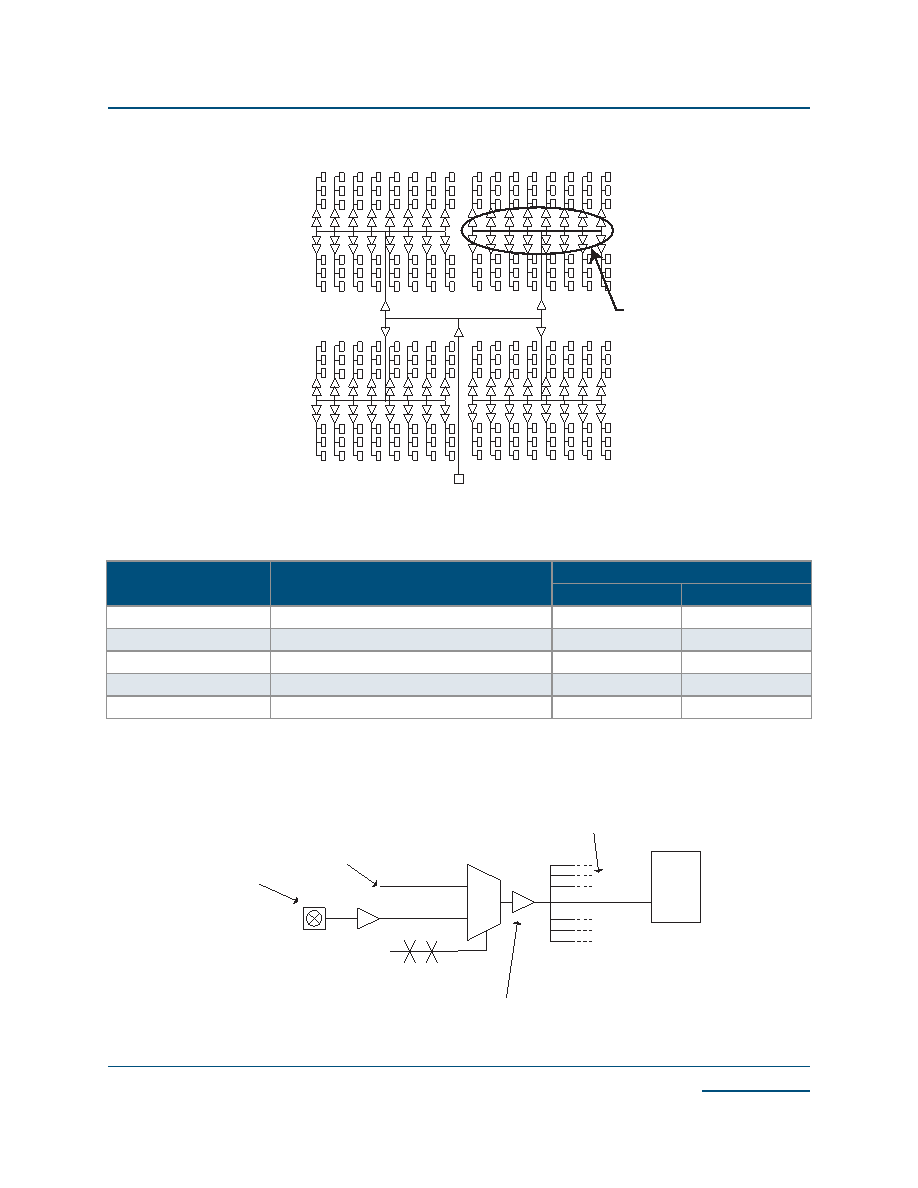

Figure 29: Eclipse-E Global Clock Structure

NOTE: When using a PLL, t

PGCK and tBGCK are effectively zero due to delay adjustment by Phase Locked

Loop feedback path.

Figure 30: Global Clock Structure Timing Elements

Table 15: Eclipse-E Tree Clock Delay

Clock Segment

Parameter

Value

Min

Max

tPGCK

Global clock pin delay to quad net

-

1.92 ns

tBGCK

Global clock tree delay (quad net to flip-flop)

-

0.28 ns

tDPD

Dedicated clock pad

-

1.7 ns

tGSKEW

Global delay clock skew

-

0.1 ns

tDSKEW

Dedicated clock skew

-

0.05 ns

Quad net

Internally generated clock, or

clock from general routing network

Global Clock

(CLK) Input

Quad-Net Clock Network

FF

Global Clock Buffer

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| QL6250E-7PS484C | FPGA, 960 CLBS, 248160 GATES, PBGA484 |

| QL6250E-7PS484I | FPGA, 960 CLBS, 248160 GATES, PBGA484 |

| QL6250E-7PS484M | FPGA, 960 CLBS, 248160 GATES, PBGA484 |

| QL6250E-8PQ208C | FPGA, 960 CLBS, 248160 GATES, PQFP208 |

| QL6250E-8PQ208I | FPGA, 960 CLBS, 248160 GATES, PQFP208 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| QL6325PQ208 | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:ASIC |

| QL6325PT280 | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:ASIC |

| QL63D5SA | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:InGaAlP Laser Diode |

| QL63F5SA | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:InGaAlP Laser Diode |

| QL63H5S-A | 制造商:ROITHNER 制造商全稱(chēng):ROITHNER 功能描述:INGaAIP Laser Diode |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。