- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378056 > PM7389 (PMC-Sierra, Inc.) Frame Engine and Datalink Manager PDF資料下載

參數(shù)資料

| 型號: | PM7389 |

| 廠商: | PMC-Sierra, Inc. |

| 英文描述: | Frame Engine and Datalink Manager |

| 中文描述: | 框架引擎和數(shù)據(jù)鏈管理 |

| 文件頁數(shù): | 2/2頁 |

| 文件大?。?/td> | 59K |

| 代理商: | PM7389 |

Head Office:

PMC-Sierra, Inc.

8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

Frame Engine and Datalink Manager

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

All product documentation is

available on our web site at:

http://www.pmc-sierra.com

For corporate information,

send email to:

info@pmc-sierra.com

PMC-1991477 (r2)

Copyright PMC-Sierra, Inc. 2001. All rights reserved.

S/UNI is a registered trademark of PMC-Sierra. Any-PHY,

SPECTRA-622, TEMUX-84, FREEDM-84A1024, AAL1gator,

SBI, and PMC-Sierra are trademarks of PMC-Sierra, Inc.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS

’

INTERNAL USE

Preliminary

PM7389 FREEDM 84A1024

HDLC

Support for up to 1024 bidirectional

HDLC channels, with individual HDLC

channel speeds ranging from 56 Kbit/s

to 52 Mbit/s. In a channelized

application, the number of time-slots

assigned to an HDLC channel is

programmable from 1 to 24 (for T1/J1)

and from 1 to 31 (for E1).

The 1024 HDLC channels can be

assigned to a mixture of physical links

via the 19.44 MHz SBI interface. The

SBI transports the equivalent of 3 STS-

1 synchronous payload envelopes

(SPE). Each STS-1 SPE can be

individually configured to carry 28

T1/J1s, 21 E1s or 1 DS3.

For each channel, supports

programmable flag sequence detection

and generation, bit stuffing and de-

stuffing, and validation and generation

of either CRC-CCITT or CRC-32 frame

check sequences.

For each channel, the receiver checks

for packet abort sequences, octet

aligned packet length and for minimum

and maximum packet length.

INTERFACES

52 MHz 16 bit Any-PHY Level 2 packet

interface for transfer of packet, frame

or fragment data using an external

controller. The interface is capable of

supporting full datagram transfer on a

per Any-PHY channel basis, or

fragmented packets or frames on a per

Any-PHY channel basis.

A 19.44 MHz SBI bus supporting up to

84 links.

3 separate clock and data interfaces to

support 3 links of arbitrary data rate up

to 52 MHz (e.g., DS3/E3). The device

can be configured to process data from

either the clock and data interfaces or

from the SBI on a per clock-data-

link/SPE basis.

A 100 MHz, 48-bit SDRAM interface

for ingress and egress per

packet/fragment storage.

A 100 MHz, 32-bit SDRAM interface

for ingress re-sequencing data.

structures.

A 100 MHz, 36-bit SSRAM interface

for Ingress/Egress Context storage.

Provides a standard 5 signal P1149.1

JTAG test port for boundary scan.

A 32-bit microprocessor interface for

configuration and status monitoring.

TECHNOLOGIES

40 mm x 40 mm, 520 pin (1.27 mm

pitch) enhanced ball grid array (SBGA)

package.

Low power 0.18 mm CMOS

technology using 1.8 V core power and

3.3 V I/O.

APPLICATIONS

IETF PPP interfaces for routers.

Frame Relay interfaces for ATM or

Frame Relay switches and

multiplexers.

Internet/Intranet access equipment.

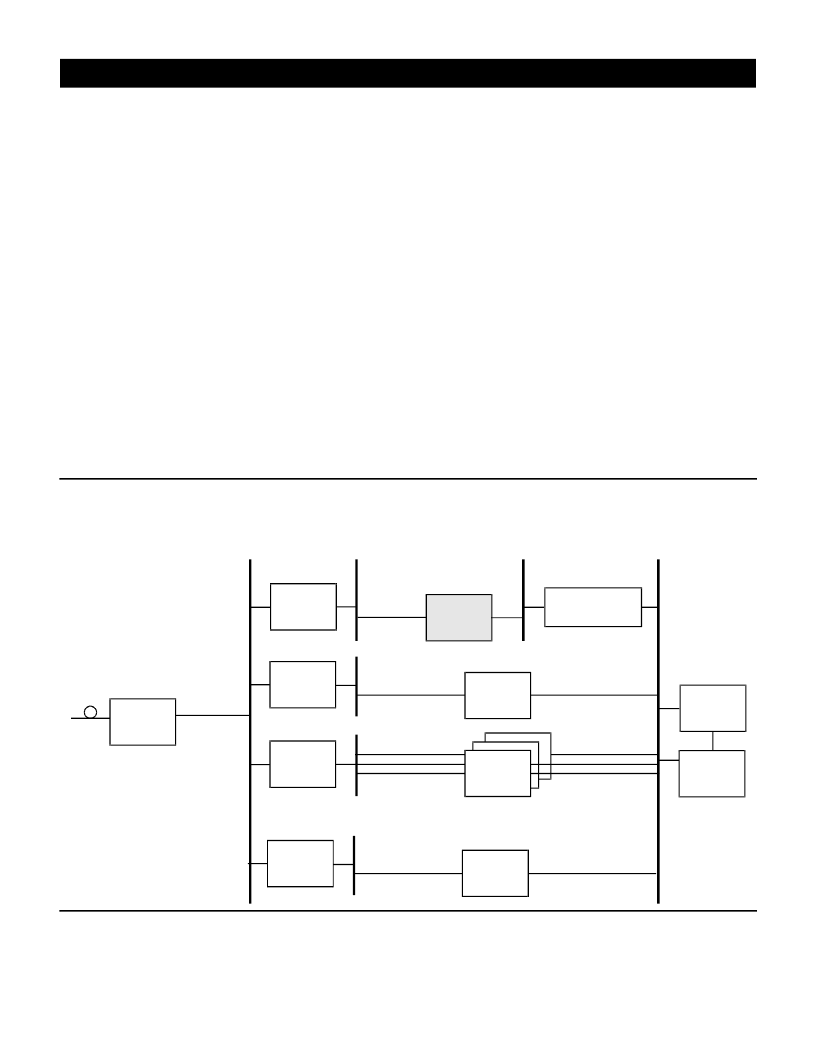

TYPICAL APPLICATION

OC-12 MULTISERVICE ARCHITECTURE

PM73122

AAL132

32

PAAL1gator-

AAL1g32

OC-12

TelecomBus

SBI

Any-PHY

(Packet)

Any-PHY

(Cell)

PM5313

SPECTRA-

622

PM7341

S/UNI-IMA-

84

PM7389

FREEDM-

84A1024

Packet/Cell

Internetworking

Function

A

A

PM7324

S/UNI-

ATLAS

PM7326

S/UNI-APEX

PM8316

TEMUX-84

PM8316

TEMUX-84

PM8316

TEMUX-84

VoATM DSP

PM8316

TEMUX-84

H-MVIP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PM7800 | Digital Correction Signal Processor |

| PM7830 | Baseband Radio Interface Controller |

| PM8172 | PM8172 System Controller |

| PM8310 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| PM8311 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PM7389-BI | 制造商:Rochester Electronics LLC 功能描述: 制造商:PMC-Sierra 功能描述:Electronic Component |

| PM7389-BI-P | 制造商:PMC-Sierra 功能描述:Electronic Component |

| PM7390-BI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。