- 您現在的位置:買賣IC網 > PDF目錄369995 > PF48F4444PPVBQ0 (INTEL CORP) Intel StrataFlash Embedded Memory PDF資料下載

參數資料

| 型號: | PF48F4444PPVBQ0 |

| 廠商: | INTEL CORP |

| 元件分類: | PROM |

| 英文描述: | Intel StrataFlash Embedded Memory |

| 中文描述: | 64M X 16 FLASH 1.8V PROM, 88 ns, PBGA80 |

| 封裝: | 11 X 11 MM, 1.40 MM HEIGHT, LEAD FREE, SCSP-88/80 |

| 文件頁數: | 46/102頁 |

| 文件大小: | 1609K |

| 代理商: | PF48F4444PPVBQ0 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁當前第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁

1-Gbit P30 Family

April 2005

46

Intel StrataFlash

Embedded Memory (P30)

Order Number: 306666, Revision: 001

Datasheet

8.0

Power and Reset Specifications

8.1

Power Up and Down

Power supply sequencing is not required if VCC, VCCQ, and VPP are connected together; If

VCCQ and/or VPP are not connected to the VCC supply, then V

CC

should attain V

CCMIN

before

applying V

CCQ

and V

PP

. Device inputs should not be driven before supply voltage equals V

CCMIN

.

Power supply transitions should only occur when RST# is low. This protects the device from

accidental programming or erasure during power transitions.

8.2

Reset Specifications

Asserting RST# during a system reset is important with automated program/erase devices because

systems typically expect to read from flash memory when coming out of reset. If a CPU reset

occurs without a flash memory reset, proper CPU initialization may not occur. This is because the

flash memory may be providing status information, instead of array data as expected. Connect

RST# to the same active low reset signal used for CPU initialization.

Also, because the device is disabled when RST# is asserted, it ignores its control inputs during

power-up/down. Invalid bus conditions are masked, providing a level of memory protection.

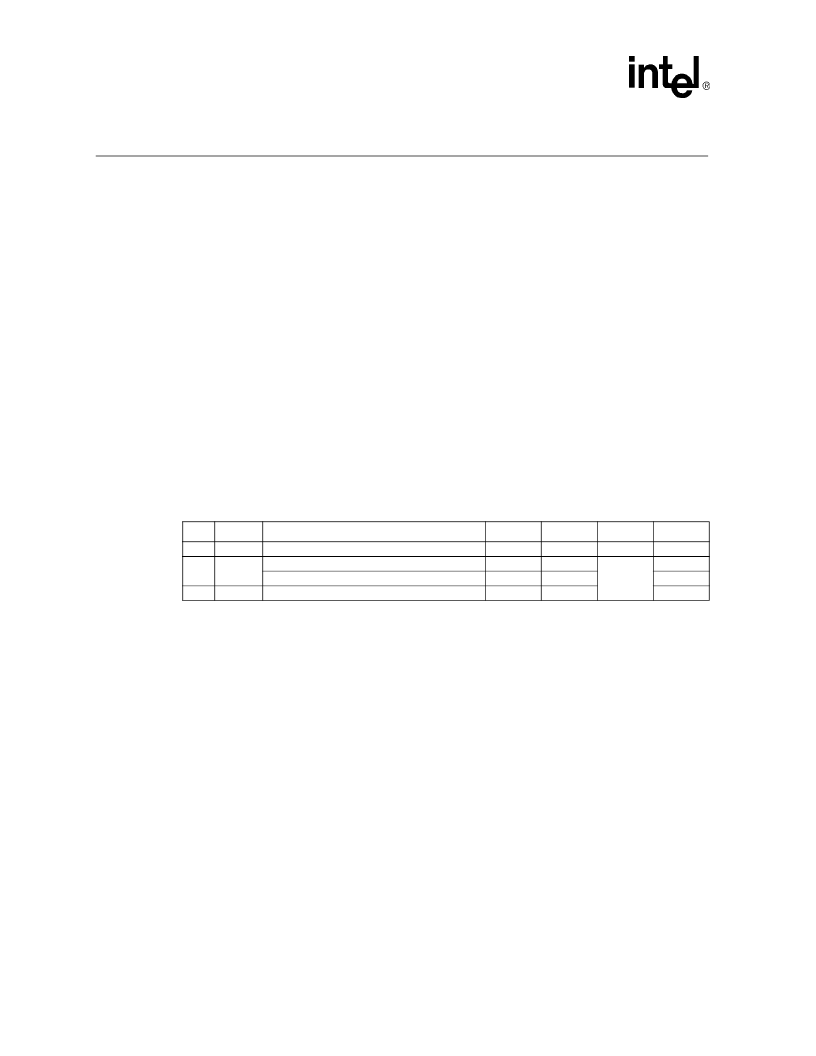

Num Symbol

P1

t

PLPH

Parameter

Min

100

-

-

60

Max

-

25

25

-

Unit

ns

Notes

1,2,3,4

1,3,4,7

1,3,4,7

1,4,5,6

RST# pulse width low

RST# low to device reset during erase

RST# low to device reset during program

V

CC

Power valid to RST# de-assertion (high)

P2

t

PLRH

μs

P3

t

VCCPH

Notes:

1.

2.

3.

4.

5.

6.

These specifications are valid for all device versions (packages and speeds).

The device may reset if t

is < t

PLPH

MIN, but this is not guaranteed.

Not applicable if RST# is tied to Vcc.

Sampled, but not 100% tested.

If RST# is tied to the V

supply, device will not be ready until t

after V

≥

V

.

If RST# is tied to any supply/signal with V

CCQ

voltage levels, the RST# input voltage must not exceed

V

until V

≥

V

.

Reset completes within t

PLPH

if RST# is asserted while no erase or program operation is executing.

7.

相關PDF資料 |

PDF描述 |

|---|---|

| PF48F2P0VBQ0 | Intel StrataFlash Embedded Memory |

| PF48F3P0VBQ0 | Intel StrataFlash Embedded Memory |

| PF48F4P0VBQ0 | Intel StrataFlash Embedded Memory |

| PF48F0P0VB00 | Intel StrataFlash Embedded Memory |

| PF48F2P0VB00 | Intel StrataFlash Embedded Memory |

相關代理商/技術參數 |

參數描述 |

|---|---|

| PF48F4444PPVTQ0 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F4P0VB00 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F4P0VBQ0 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F4P0VT00 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F4P0VTQ0 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

發(fā)布緊急采購,3分鐘左右您將得到回復。