- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369986 > PDU1064H Programmable 6-bit 10K ECL delay line PDF資料下載

參數(shù)資料

| 型號(hào): | PDU1064H |

| 英文描述: | Programmable 6-bit 10K ECL delay line |

| 中文描述: | 可編程6位10,000 ECL延遲線 |

| 文件頁(yè)數(shù): | 1/5頁(yè) |

| 文件大小: | 69K |

| 代理商: | PDU1064H |

PDU1016H

Doc #97044

DATA DELAY DEVICES, INC.

3 Mt. Prospect Ave. Clifton, NJ 07013

1

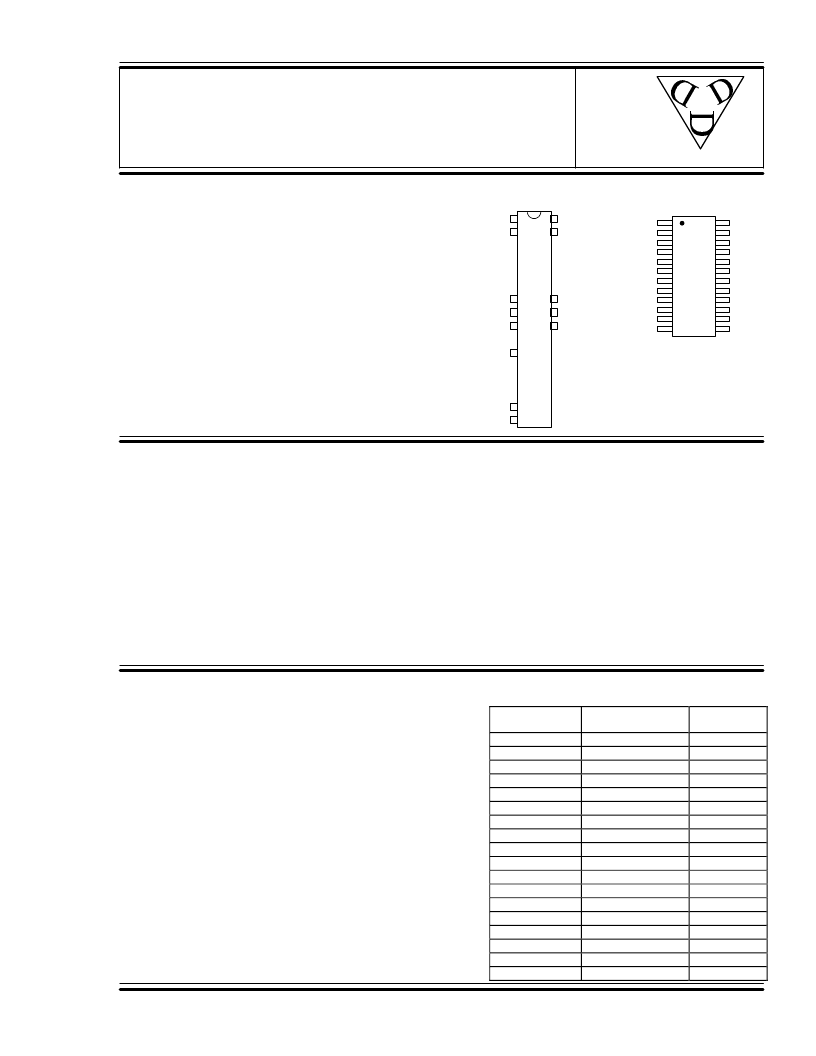

4-BIT, ECL-INTERFACED

PROGRAMMABLE DELAY LINE

(SERIES PDU1016H)

FEATURES

PACKAGES

Digitally programmable in 16 delay steps

Monotonic delay-versus-address variation

Precise and stable delays

Input & outputs fully 10KH-ECL interfaced & buffered

Fits 32-pin DIP socket

FUNCTIONAL DESCRIPTION

The PDU1016H-series device is a 4-bit digitally programmable delay line.

The delay, TD

A

, from the input pin (IN) to the output pin (OUT) depends

on the address code (A3-A0) according to the following formula:

TD

A

= TD

0

+ T

INC

* A

where A is the address code, T

INC

is the incremental delay of the device, and TD

0

is the inherent delay of

the device. The incremental delay is specified by the dash number of the device and can range from

0.5ns through 100ns, inclusively. The enable pin (ENB) is held LOW during normal operation. When this

signal is brought HIGH, OUT is forced into a LOW state. The address is not latched and must remain

asserted during normal operation.

SERIES SPECIFICATIONS

Total programmed delay tolerance:

5% or 1ns,

whichever is greater

Inherent delay (TD

0

):

5.5ns typical for dash numbers

up to 5, greater for larger #’s

Setup time and propagation delay:

Address to input setup (T

AIS

):

Disable to output delay (T

DISO

):

1.7ns typical

Operating temperature:

0

°

to 70

°

C

Temperature coefficient:

100PPM/

°

C (excludes TD

0

)

Supply voltage V

EE

:

-5VDC

±

5%

Power Dissipation:

615mw typical (no load)

Minimum pulse width:

20% of total delay

3.6ns

1997 Data Delay Devices

data

delay

devices,

inc.

3

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

N/C

N/C

OUT

GND

ENB

N/C

N/C

N/C

GND

ENB

N/C

IN

N/C

A2

A1

VEE

A0

N/C

N/C

N/C

VEE

A3

N/C

N/C

32

31

26

25

24

1

2

7

8

9

11

15

16

GND

ENB

A0

VEE

GND

IN

A3

VEE

GND

OUT

A1

A2

GND

PDU1016H-xxC4

PDU1016H-xxMC4 Mil SMD

SMD

PDU1016H-xx

PDU1016H-xxM Mil DIP

DIP

PIN DESCRIPTIONS

IN

OUT

A0-A3 Address Bits

ENB

Output Enable

VEE

-5 Volts

GND

Ground

Signal Input

Signal Output

DASH NUMBER SPECIFICATIONS

Part

Number

PDU1016H-.5

PDU1016H-1

PDU1016H-2

PDU1016H-3

PDU1016H-4

PDU1016H-5

PDU1016H-6

PDU1016H-8

PDU1016H-10

PDU1016H-15

PDU1016H-20

PDU1016H-25

PDU1016H-30

PDU1016H-40

PDU1016H-50

PDU1016H-60

PDU1016H-80

PDU1016H-100

Incremental Delay

Per Step (ns)

0.5

±

0.3

1.0

±

0.5

2.0

±

0.5

3.0

±

1.0

4.0

±

1.0

5.0

±

1.0

6.0

±

1.0

8.0

±

1.0

10.0

±

1.5

15.0

±

1.5

20.0

±

2.0

25.0

±

2.5

30.0

±

3.0

40.0

±

4.0

50.0

±

5.0

60.0

±

6.0

80.0

±

8.0

100.0

±

10.0

Total

Delay (ns)

7.5

±

1.0

15

±

1.0

30

±

1.5

45

±

2.2

60

±

3.0

75

±

3.7

90

±

4.5

120

±

6.0

150

±

7.5

225

±

11.2

300

±

15.0

375

±

18.8

450

±

22.5

600

±

30.0

750

±

37.5

900

±

45.0

1200

±

60.0

1500

±

75.0

NOTE: Any dash number between .5 and 100

not shown is also available.

Powered by ICminer.com Electronic-Library Service CopyRight 2003

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PDU1064HSERIES | 6-BIT. ECL-INTERFACED PROGRAMMABLE DELAY LINE |

| PDU10256H-.5 | 8-BIT, ECL-INTERFACED PROGRAMMABLE DELAY LINE (SERIES PDU10256H) |

| PDU10256H-.5C5 | 8-BIT, ECL-INTERFACED PROGRAMMABLE DELAY LINE (SERIES PDU10256H) |

| PDU10256H-.5M | 8-BIT, ECL-INTERFACED PROGRAMMABLE DELAY LINE (SERIES PDU10256H) |

| PDU10256H-.5MC5 | 8-BIT, ECL-INTERFACED PROGRAMMABLE DELAY LINE (SERIES PDU10256H) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PDU1064H-.5 | 制造商:DATADELAY 制造商全稱(chēng):Data Delay Devices, Inc. 功能描述:6-BIT, ECL-INTERFACED PROGRAMMABLE DELAY LINE (SERIES PDU1064H) |

| PDU1064H-.5C5 | 制造商:DATADELAY 制造商全稱(chēng):Data Delay Devices, Inc. 功能描述:6-BIT, ECL-INTERFACED PROGRAMMABLE DELAY LINE (SERIES PDU1064H) |

| PDU1064H-.5M | 制造商:DATADELAY 制造商全稱(chēng):Data Delay Devices, Inc. 功能描述:6-BIT, ECL-INTERFACED PROGRAMMABLE DELAY LINE (SERIES PDU1064H) |

| PDU1064H-.5MC5 | 制造商:DATADELAY 制造商全稱(chēng):Data Delay Devices, Inc. 功能描述:6-BIT, ECL-INTERFACED PROGRAMMABLE DELAY LINE (SERIES PDU1064H) |

| PDU-1064H-0.5 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Programmable Delay Line |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。