- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369960 > PDI1394P23BD (NXP SEMICONDUCTORS) 2-port/1-port 400 Mbps physical layer interface PDF資料下載

參數(shù)資料

| 型號: | PDI1394P23BD |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2-port/1-port 400 Mbps physical layer interface |

| 中文描述: | 2 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP64 |

| 封裝: | 10 X 10 X 1.40 MM, PLASTIC, LQFP-64 |

| 文件頁數(shù): | 33/42頁 |

| 文件大?。?/td> | 233K |

| 代理商: | PDI1394P23BD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

Philips Semiconductors

Preliminary data

PDI1394P23

2-port/1-port 400 Mbps physical layer interface

2001 Sep 06

33

Table 20. LPS Timing Parameters

PARAMETER

DESCRIPTION

MIN

MAX

UNIT

T

LPSL

T

LPSH

LPS low time (when pulsed) (see Note 1)

0.09

2.60

μ

S

LPS high time (when pulsed) (see Note 1)

0.021

2.60

μ

S

LPS duty cycle (when pulsed) (see Note 2)

20

55

%

T

LPS_RESET

T

LPS_DISABLE

T

RESTORE

T

CLK_ACTIVATE

Time for PHY to recognize LPS deasserted and reset the interface

2.60

2.68

μ

S

Time for PHY to recognize LPS deasserted and disable the interface

26.03

26.11

23

3

μ

S

Time to permit optional isolation circuits to restore during an interface reset

15

μ

S

Time for SYSCLK to be activated from reassertion of LPS

—

60

nS

NOTES:

1. The specified T

LPSL

and T

LPSH

times are worst–case values appropriate for operation with the PDI1394P23. These values are broader than

those specified for the same parameters in the P1394a Supplement (i.e., an implementation of LPS that meets the requirements of P1394a

will operate correctly with the PDI1394P23).

2. A pulsed LPS signal must have a duty cycle (ratio of T

to cycle period) in the specified range to ensure proper operation when using an

isolation barrier on the LPS signal (e.g., as shown in Figure 8)

3. The maximum value for T

does not apply when the PHY–LLC interface is disabled, in which case an indefinite time may elapse

before LPS is reasserted. Otherwise, in order to reset but not disable the interface it is necessary that the LLC ensure that LPS is

deasserted for less than T

LPS_DISABLE

.

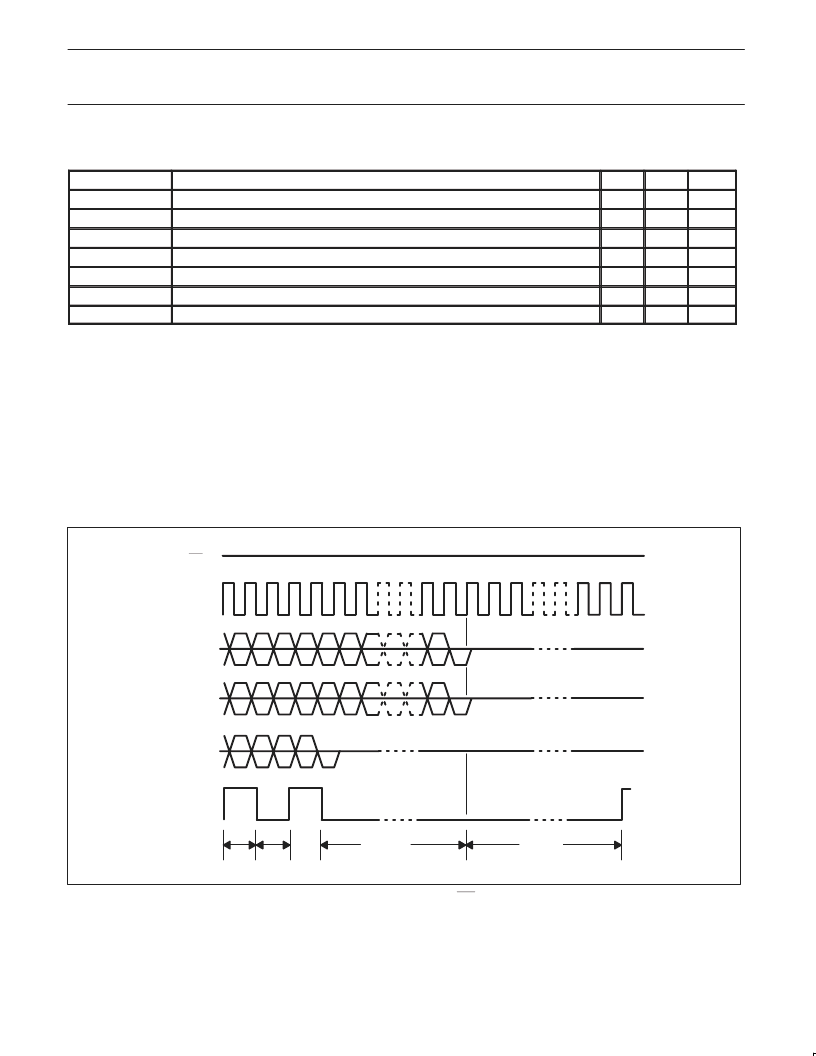

The LLC requests that the interface be reset by deasserting the LPS

signal and terminating all bus and request activity. When the PHY

observes that LPS has been deasserted for T

LPS_RESET

, it resets

the interface. When the interface is in the reset state, the PHY sets

its CTL and D outputs in the logic 0 state and ignores any activity on

the LREQ signal. The timing for interface reset is shown in Figure 20

and Figure 21.

T

LPS_RESET

T

RESTORE

ISO

SYSCLK

CTL0, CTL1

D0 – D7

LREQ

LPS

(low)

(a)

(c)

(d)

(b)

T

LPSL

T

LPSH

SV01810

Figure 20.

Interface Reset, ISO Low

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PDI1394L41BE | 8358 PBGA ENCRP NO-PB |

| PDI1394P21BE | 3-port physical layer interface |

| PDI1394P22BD | 3-port physical layer interface |

| PDI1394L11BA | 1394 AV link layer controller |

| PDI1394L21BE | 1394 full duplex AV link layer controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PDI1394P23BD,118 | 功能描述:輸入/輸出控制器接口集成電路 1394 2-PORT PHY NO NEW DESIGNS RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| PDI1394P23BD,151 | 功能描述:輸入/輸出控制器接口集成電路 DO NOT USE ORDER -T PART RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| PDI1394P23BD,157 | 功能描述:輸入/輸出控制器接口集成電路 IEEE1394A 2 PORT PHY RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| PDI1394P23BD-S | 功能描述:輸入/輸出控制器接口集成電路 DO NOT USE ORDER-T PART RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| PDI1394P23BD-T | 功能描述:輸入/輸出控制器接口集成電路 1394 2-PORT PHY NO NEW DESIGNS RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。