- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369960 > PDI1394P23BD (NXP SEMICONDUCTORS) 2-port/1-port 400 Mbps physical layer interface PDF資料下載

參數(shù)資料

| 型號: | PDI1394P23BD |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2-port/1-port 400 Mbps physical layer interface |

| 中文描述: | 2 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP64 |

| 封裝: | 10 X 10 X 1.40 MM, PLASTIC, LQFP-64 |

| 文件頁數(shù): | 28/42頁 |

| 文件大?。?/td> | 233K |

| 代理商: | PDI1394P23BD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當(dāng)前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

Philips Semiconductors

Preliminary data

PDI1394P23

2-port/1-port 400 Mbps physical layer interface

2001 Sep 06

28

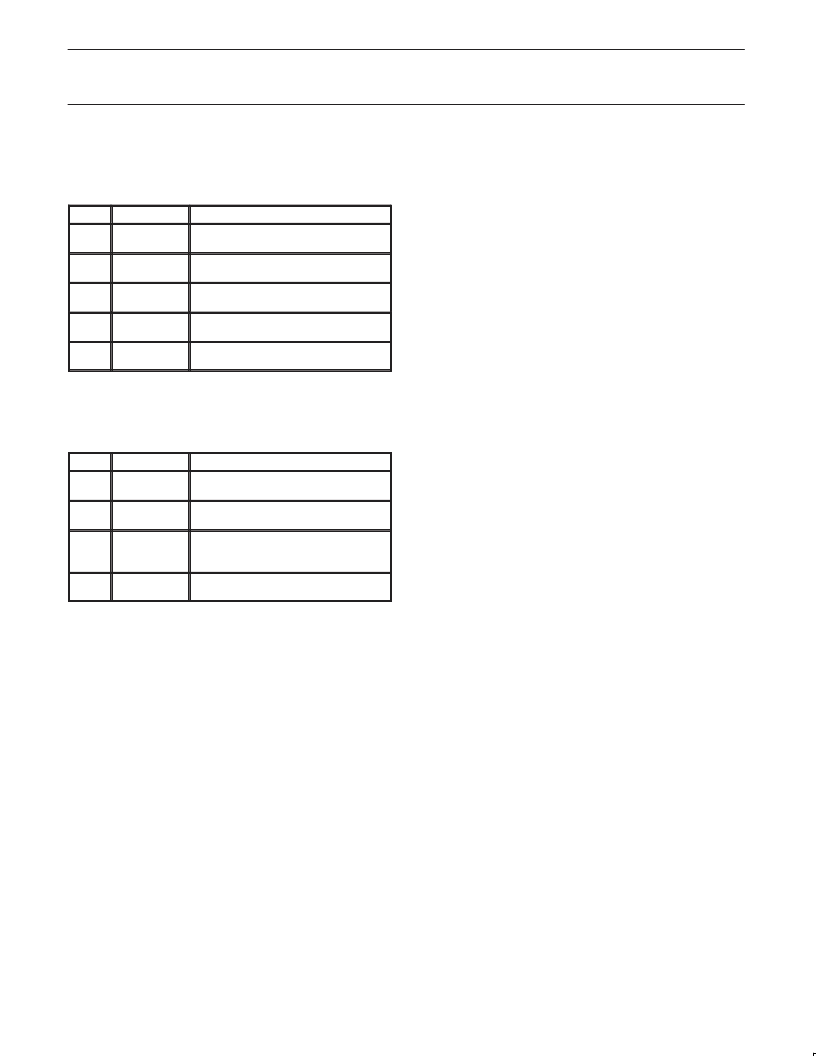

For a write register request, the length of the LREQ bit stream is

17 bits as shown in Table 16.

Table 16. Write Register Request

BIT(S)

NAME

DESCRIPTION

0

Start Bit

Indicates the beginning of the transfer

(always 1).

A 101 indicating that this is a write

register request.

Identifies the address of the PHY

register to be written to.

Gives the data that is to be written to the

specified register address.

Indicates the end of the transfer

(always 0).

1–3

Request Type

4–7

Address

8–15

Data

16

Stop Bit

For an acceleration control request, the length of the LREQ data

stream is 6 bits as shown in Table 17.

Table 17. Acceleration Control Request

BIT(S)

NAME

DESCRIPTION

0

Start Bit

Indicates the beginning of the transfer

(always 1).

A 110 indicating this is an acceleration

control request.

Asynchronous period arbitration

acceleration is enabled if 1, and

disabled if 0.

1–3

Request Type

4

Control

5

Stop Bit

Indicates the end of the transfer

(always 0).

For fair or priority access, the LLC sends the bus request (FairReq or

PriReq) at least one clock after the PHY-LLC interface becomes idle. If

the CTL terminals are asserted to the receive state (10b) by the PHY,

then any pending fair or priority request is lost (cleared). Additionally,

the PHY ignores any fair or priority requests if the Receive state is

asserted while the LLC is sending the request. The LLC may then

reissue the request one clock after the next interface idle.

The cycle master node uses priority bus request (PriReq) to send a

cycle start packet. After receiving or transmitting a cycle start

packet, the LLC can issue an isochronous bus request (IsoReq).

The PHY will clear an isochronous request only when the bus has

been won.

To send an acknowledge packet, the link must issue an immediate

bus request (ImmReq) during the reception of the packet addressed

to it. This is required in order to minimize the idle gap between the

end of the received packet and the start of the transmitted

acknowledge packet. As soon as the receive packet ends, the PHY

immediately grants control of the bus to the LLC. The LLC sends an

acknowledgment to the sender unless the header CRC of the

received packet is corrupted. In this case, the LLC does not transmit

an acknowledge, but instead cancels the transmit operation and

releases the interface immediately; the LLC must not use this grant

to send another type of packet. After the interface is released, the

LLC may proceed with another request.

The LLC may request only one bus request at a time. Once the LLC

issues any request for bus access (ImmReq, IsoReq, FairReq, or

PriReq), it cannot issue another request until the PHY indicates that

the bus request was “l(fā)ost” (bus arbitration lost and another packet

received), or “won” (bus arbitration won and the LLC granted

control). The PHY ignores new bus requests while a previous bus

request is pending. All bus requests are cleared upon a bus reset.

For write register requests, the PHY loads the specified data into the

addressed register as soon as the request transfer is complete. For

read register requests, the PHY returns the contents of the

addressed register to the LLC at the next opportunity through a

status transfer. If a received packet interrupts the status transfer,

then the PHY continues to attempt the transfer of the requested

register until it is successful. A write or read register request may be

made at any time, including while a bus request is pending. Once a

read register request is made, the PHY ignores further read register

requests until the register contents are successfully transferred to

the LLC. A bus reset does not clear a pending read register request.

The PDI1394P23 includes several arbitration acceleration

enhancements which allow the PHY to improve bus performance

and throughput by reducing the number and length of inter-packet

gaps. These enhancements include autonomous (fly-by)

isochronous packet concatenation, autonomous fair and priority

packet concatenation onto acknowledge packets, and accelerated

fair and priority request arbitration following acknowledge packets.

Then enhancements are enabled when the EAA bit in PHY

register 5 is set.

The arbitration acceleration enhancements may interfere with the

ability of the cycle master node to transmit the cycle start packet

under certain circumstances. The acceleration control request is

therefore provided to allow the LLC to temporarily enable or disable

the arbitration acceleration enhancements of the PDI1394P23

during the asynchronous period. The LLC typically disables the

enhancements when its internal cycle counter rolls over indicating

that a cycle start packet is imminent, and then re-enables the

enhancements when it receives a cycle start packet. The

acceleration control request may be made at any time, however, and

is immediately serviced by the PHY. Additionally, a bus reset or

isochronous bus request will cause the enhancements to be

re-enabled, if the EAA bit is set.

18.2

A status transfer is initiated by the PHY when there is status

information to be transferred to the LLC. The PHY waits until the

interface is idle before starting the transfer. The transfer is initiated

by the PHY asserting Status (01b) on the CTL terminals, along with

the first two bits of status information on the D[0:1] terminals. The

PHY maintains CTL = Status for the duration of the status transfer.

The PHY may prematurely end a status transfer by asserting

something other than Status on the CTL terminals. This occurs if a

packet is received before the status transfer completes. The PHY

continues to attempt to complete the transfer until all status

information has been successfully transmitted. There is at least one

idle cycle between consecutive status transfers.

Status transfer

The PHY normally sends just the first four bits of status to the LLC.

These bits are status flags that are needed by the LLC state

machines. The PHY sends an entire 16-bit status packet to the LLC

after a read register request, or when the PHY has pertinent

information to send to the LLC or transaction layers. The only

defined condition where the PHY automatically sends a register to

the LLC is after self-ID, where the PHY sends the physical-ID

register that contains the new node address. All status transfers are

either 4 or 16 bits unless interrupted by a received packet. The

status flags are considered to have been successfully transmitted to

the LLC immediately upon being sent, even if a received packet

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PDI1394L41BE | 8358 PBGA ENCRP NO-PB |

| PDI1394P21BE | 3-port physical layer interface |

| PDI1394P22BD | 3-port physical layer interface |

| PDI1394L11BA | 1394 AV link layer controller |

| PDI1394L21BE | 1394 full duplex AV link layer controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PDI1394P23BD,118 | 功能描述:輸入/輸出控制器接口集成電路 1394 2-PORT PHY NO NEW DESIGNS RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| PDI1394P23BD,151 | 功能描述:輸入/輸出控制器接口集成電路 DO NOT USE ORDER -T PART RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| PDI1394P23BD,157 | 功能描述:輸入/輸出控制器接口集成電路 IEEE1394A 2 PORT PHY RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| PDI1394P23BD-S | 功能描述:輸入/輸出控制器接口集成電路 DO NOT USE ORDER-T PART RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| PDI1394P23BD-T | 功能描述:輸入/輸出控制器接口集成電路 1394 2-PORT PHY NO NEW DESIGNS RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。