- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367822 > PCI9060ES (Electronic Theatre Controls, Inc.) 12O COMPATIBLE PCI BUS MASTER INTERFACE CHIP FOR ADAPTERS AND EMBEDDED SYSTEMS PDF資料下載

參數(shù)資料

| 型號(hào): | PCI9060ES |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 12O COMPATIBLE PCI BUS MASTER INTERFACE CHIP FOR ADAPTERS AND EMBEDDED SYSTEMS |

| 中文描述: | 12O兼容的PCI總線主控接口芯片的適配器和嵌入式系統(tǒng) |

| 文件頁(yè)數(shù): | 32/192頁(yè) |

| 文件大?。?/td> | 1551K |

| 代理商: | PCI9060ES |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)當(dāng)前第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)

SECTION 3

PCI 9080

FUNCTIONAL DESCRIPTION

PLX Technology, Inc., 1997

Page 23

Version 1.02

3.6.2 Direct Slave Operation (PCI Master to

Local Bus Access)

PCI 9080 supports both burst memory mapped transfer

accesses and I/O-mapped, single-transfer accesses to

the local bus from the PCI bus. PCI Base Address

registers are provided to set up the location of the

adapter in PCI memory and I/O space. In addition, local

mapping registers allow address translation from PCI

address space to Local Address Space. There are three

spaces available:

Space 0

Space 1

Expansion ROM space

Expansion ROM space is intended to support a bootable

ROM device for the host. Each local space can be

programmed to operate 8 bit, 16 bit, or 32 bit local bus

width. PCI 9080 has an internal wait state generator and

external wait state input (READYi#). READYi# can be

disabled or enabled with the internal configuration

register. The local bus, independent of the PCI bus, can

Burst as long as data is available (Continuous Burst

mode)

Burst four Lwords at a time

Perform continuous single cycle, with or without wait

state(s)

For single cycle Direct Slave reads, PCI 9080 reads a

single local bus Lword or partial Lword. PCI 9080

disconnects after one transfer for all Direct Slave I/O

accesses.

For the highest data transfer rate, PCI 9080 supports

posted write and can be programmed to prefetch data

during PCI Burst Read. The prefetch size, when

enabled, can be one to 16 Lwords, or until the PCI stops

requesting. PCI 9080 will prefetch if enabled and drop

the local bus after the prefetch counter is reached. In a

continuous prefetch mode, PCI 9080 prefetches as long

as any FIFO space is available and terminates the

prefetch when the PCI terminates the request. If read

prefetching is disabled, PCI 9080 disconnects after one

read transfer.

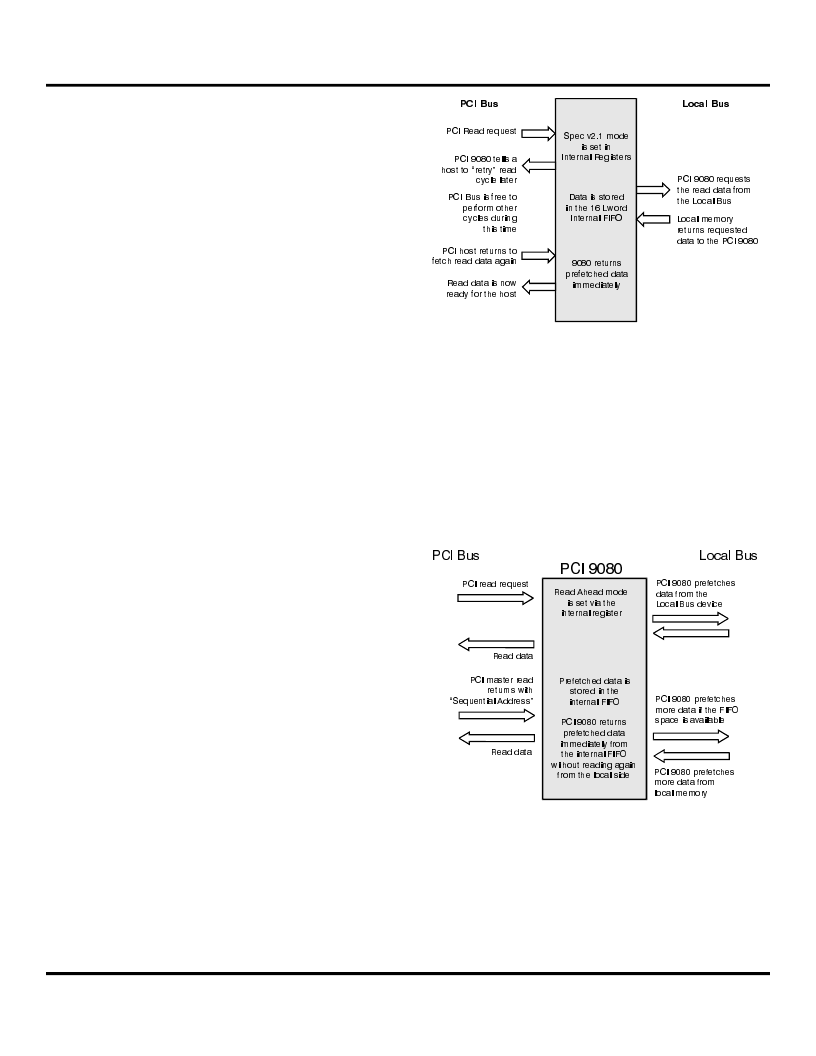

3.6.2.1 PCI 2.1 Mode

PCI 9080 can be programmed through the Local

Arbitration and PCI Mode Register to perform delayed

reads, as specified in PCI specification v2.1.

!

"

#

$% &!

$%

'#(

#

$% )! "

"

# !

$% !

"

# "

$% &!

"

)!

#

! &!

$%

Figure 3-9. PCI Specification v2.1 Delayed Reads

In addition to delayed read, PCI 9080 supports the

following in PCI specification v2.1 features.

No write while read is pending (RETRY for reads)

Write and flush pending read

PCI 9080 also supports Read Ahead mode (refer to

Figure 3-10), where prefetched data can be read from

the PCI 9080 internal FIFO instead of from the local

side. The address must be subsequent to the previous

address and must be 32-bit aligned (next address =

current address + 4).

!

!

"

##$

%

##$

" "

##$

!&

%

Figure 3-10. PCI 9080 Read Ahead Mode

PCI 9080 can be programmed to keep the PCI bus by

generating a wait state(s), de-asserting TRDY#, if write

FIFO becomes full. PCI 9080 can also be programmed

to keep the local bus, LHOLD is asserted, if Direct Slave

Write FIFO becomes empty or the Direct Slave Read

FIFO becomes full. The local bus is dropped in either

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCI9060SD | 12O COMPATIBLE PCI BUS MASTER INTERFACE CHIP FOR ADAPTERS AND EMBEDDED SYSTEMS |

| PCI950PT | PC Card Support |

| PCI9656-AC66BI | Controller Miscellaneous - Datasheet Reference |

| PCIB40 | PC(ISA)BUS I/O CARD |

| PCICLOCKGEN_R001 | AMD Alchemy? Solutions Au1500? PCI Clock Generation? |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCI9060ESF | 功能描述:數(shù)字總線開(kāi)關(guān) IC PCI Bus Interface RoHS:否 制造商:Texas Instruments 開(kāi)關(guān)數(shù)量:24 傳播延遲時(shí)間:0.25 ns 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TSSOP-56 封裝:Reel |

| PCI9060ESREV1 | 制造商:PLX Technology 功能描述: |

| PCI9060SD | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:12O COMPATIBLE PCI BUS MASTER INTERFACE CHIP FOR ADAPTERS AND EMBEDDED SYSTEMS |

| PCI9060SD-1AF | 功能描述:數(shù)字總線開(kāi)關(guān) IC PCI Bus Interface RoHS:否 制造商:Texas Instruments 開(kāi)關(guān)數(shù)量:24 傳播延遲時(shí)間:0.25 ns 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TSSOP-56 封裝:Reel |

| PCI9080 | 制造商:PLX 制造商全稱:PLX 功能描述:I2O Compatible PCI Bus Master I/O Accelerator Chip |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。