- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369948 > PC28F128J3A-110 (Intel Corp.) Intel StrataFlash Memory (J3) PDF資料下載

參數(shù)資料

| 型號: | PC28F128J3A-110 |

| 廠商: | Intel Corp. |

| 英文描述: | Intel StrataFlash Memory (J3) |

| 中文描述: | 英特爾StrataFlash存儲器(J3) |

| 文件頁數(shù): | 26/72頁 |

| 文件大小: | 905K |

| 代理商: | PC28F128J3A-110 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁

256-Mbit J3 (x8/x16)

26

Datasheet

7.2

Write Operations

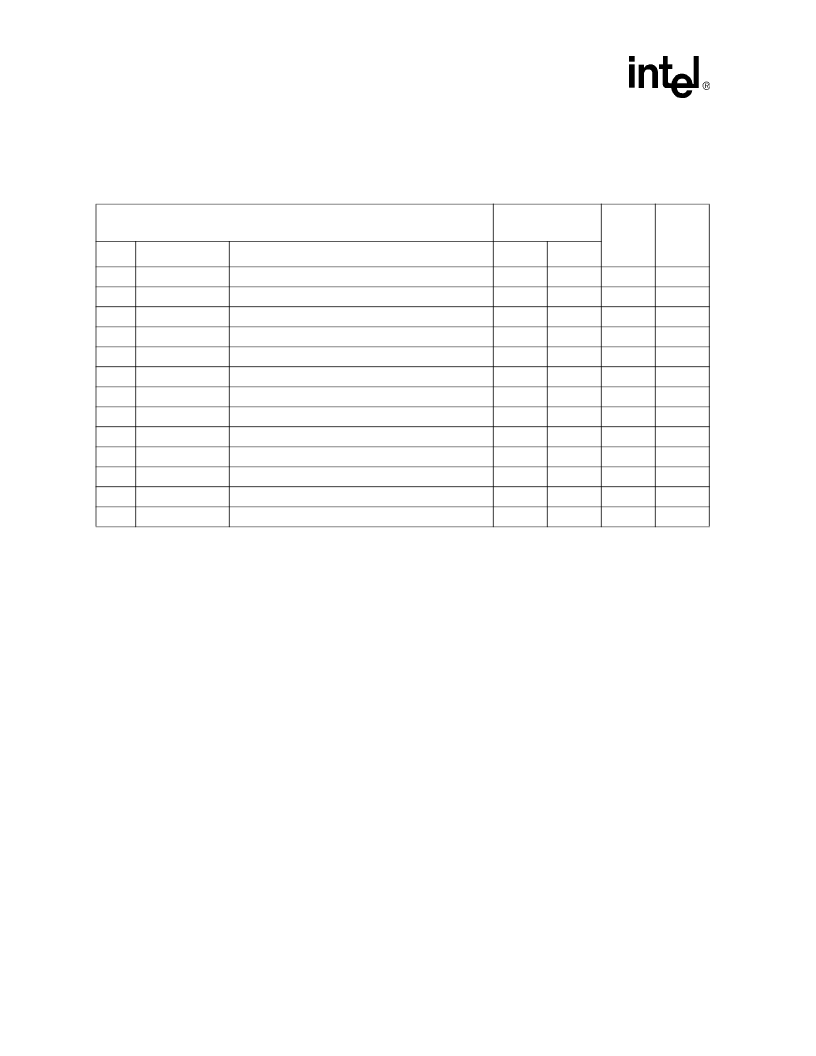

Table 9. Write Operations

Versions

Valid for All

Speeds

Unit

Notes

#

Symbol

Parameter

Min

Max

W1

t

PHWL

(t

PHEL

)

RP# High Recovery to WE# (CE

X

) Going Low

1

μs

1,2,3

W2

t

ELWL

(t

WLEL

)

t

WP

CE

X

(WE#) Low to WE# (CE

X

) Going Low

Write Pulse Width

0

ns

1,2,4

W3

70

ns

1,2,4

W4

t

DVWH

(t

DVEH

)

Data Setup to WE# (CE

X

) Going High

50

ns

1,2,5

W5

t

AVWH

(t

AVEH

)

t

WHEH

(t

EHWH

)

Address Setup to WE# (CE

X

) Going High

CE

X

(WE#) Hold from WE# (CE

X

) High

55

ns

1,2,5

W6

0

ns

1,2,

W7

t

WHDX

(t

EHDX

)

Data Hold from WE# (CE

X

) High

0

ns

1,2,

W8

t

WHAX

(t

EHAX

)

t

WPH

Address Hold from WE# (CE

X

) High

Write Pulse Width High

0

ns

1,2,

W9

30

ns

1,2,6

W11

t

VPWH

(t

VPEH

)

V

PEN

Setup to WE# (CE

X

) Going High

0

ns

1,2,3

W12

t

WHGL

(t

EHGL

)

t

WHRL

(t

EHRL

)

Write Recovery before Read

35

ns

1,2,7

W13

WE# (CE

X

) High to STS Going Low

500

ns

1,2,8

W15

t

QVVL

V

PEN

Hold from Valid SRD, STS Going High

0

ns

1,2,3,8,9

NOTES:

CE

X

low is defined as the first edge of CE0, CE1, or CE2 that enables the device. CE

X

high is defined at the first edge of CE0, CE1,

or CE2 that disables the device (see

Table 13

).

1. Read timing characteristics during block erase, program, and lock-bit configuration operations are the same as

during read-only operations. Refer to

AC Characteristics–Read-Only Operations

.

2. A write operation can be initiated and terminated with either CE

X

or WE#.

3. Sampled, not 100% tested.

4. Write pulse width (t

WP

) is defined from CE

X

or WE# going low (whichever goes low last) to CE

X

or WE# going

high (whichever goes high first). Hence, t

WP

= t

WLWH

= t

ELEH

= t

WLEH

= t

ELWH

.

5. Refer to

Table 14

for valid A

IN

and D

IN

for block erase, program, or lock-bit configuration.

6. Write pulse width high (t

WPH

) is defined from CE

X

or WE# going high (whichever goes high first) to CE

X

or WE#

going low (whichever goes low first). Hence, t

WPH

= t

WHWL

= t

EHEL

= t

WHEL

= t

EHWL

.

7. For array access, t

AVQV

is required in addition to t

WHGL

for any accesses after a write.

8. STS timings are based on STS configured in its RY/BY# default mode.

9. V

should be held at V

PENH

until determination of block erase, program, or lock-bit configuration success

(SR[1,3,4:5] = 0).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PC28F128J3A-115 | Intel StrataFlash Memory (J3) |

| PC28F640J3C-125 | Intel StrataFlash Memory (J3) |

| PC28F640J3C-150 | Intel StrataFlash Memory (J3) |

| PC28F640J3A-110 | Intel StrataFlash Memory (J3) |

| PC28F640J3A-115 | Intel StrataFlash Memory (J3) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PC28F128J3A-115 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Memory (J3) |

| PC28F128J3A-120 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Memory (J3) |

| PC28F128J3A-125 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Memory (J3) |

| PC28F128J3A-150 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Memory (J3) |

| PC28F128J3C-110 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Memory (J3) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。