- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369945 > P89LPC932FHN (NXP SEMICONDUCTORS) 8-bit microcontroller with accelerated two-clock 80C51 core 8 kB Flash with 512-byte data EEPROM and 768-byte RAM PDF資料下載

參數(shù)資料

| 型號: | P89LPC932FHN |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-bit microcontroller with accelerated two-clock 80C51 core 8 kB Flash with 512-byte data EEPROM and 768-byte RAM |

| 中文描述: | 8-BIT, FLASH, 12 MHz, MICROCONTROLLER, PQCC28 |

| 封裝: | 6 X 6 MM, 0.85 MM HEIGHT, MO-220, SOT-788-1, PLASTIC, HVQFN-28 |

| 文件頁數(shù): | 41/64頁 |

| 文件大小: | 316K |

| 代理商: | P89LPC932FHN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當(dāng)前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

9397 750 14871

Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet

Rev. 02 — 10 May 2005

41 of 64

Philips Semiconductors

P89LPC932A1

8-bit microcontroller with accelerated two-clock 80C51 core

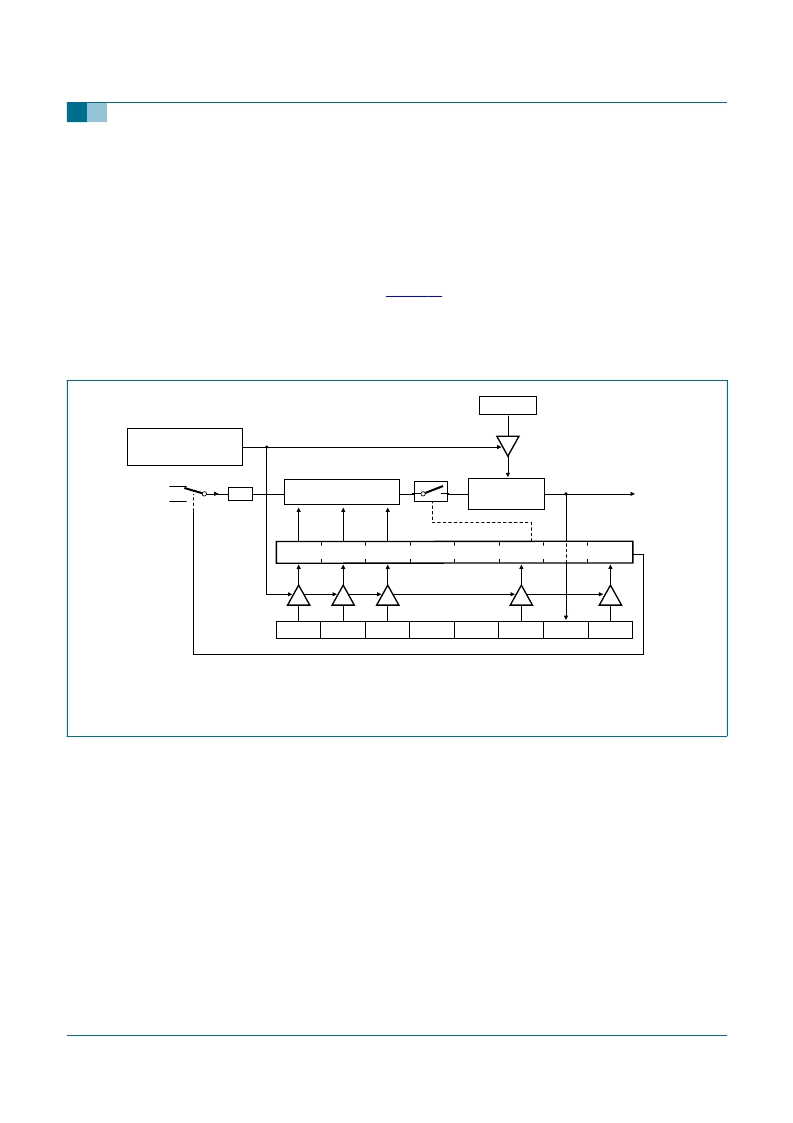

7.25 Watchdog timer

The watchdog timer causes a system reset when it underflows as a result of a failure to

feed the timer prior to the timer reaching its terminal count. It consists of a programmable

12-bit prescaler, and an 8-bit down counter. The down counter is decremented by a tap

taken from the prescaler. The clock source for the prescaler is either the PCLK or the

nominal 400 kHz watchdog oscillator. The watchdog timer can only be reset by a

power-on reset. When the watchdog feature is disabled, it can be used as an interval timer

and may generate an interrupt.

Figure 20

shows the watchdog timer in Watchdog mode.

Feeding the watchdog requires a two-byte sequence. If PCLK is selected as the watchdog

clock and the CPU is powered-down, the watchdog is disabled. The watchdog timer has a

time-out period that ranges from a few

μ

s to a few seconds. Please refer to the

P89LPC932A1 User manualfor more details.

7.26 Additional features

7.26.1

Software reset

The SRST bit in AUXR1 gives software the opportunity to reset the processor completely,

as if an external reset or watchdog reset had occurred. Care should be taken when writing

to AUXR1 to avoid accidental software resets.

7.26.2

Dual data pointers

The dual Data Pointers (DPTR) provides two different Data Pointers to specify the address

used with certain instructions. The DPS bit in the AUXR1 register selects one of the two

Data Pointers. Bit 2 of AUXR1 is permanently wired as a logic 0 so that the DPS bit may

be toggled (thereby switching Data Pointers) simply by incrementing the AUXR1 register,

without the possibility of inadvertently altering other bits in the register.

(1) Watchdog reset can also be caused by an invalid feed sequence, or by writing to WDCON not immediately followed by a

feed sequence.

Fig 20. Watchdog timer in Watchdog mode (WDTE = 1).

PRE2

PRE1

PRE0

-

-

WDRUN

WDTOF

WDCLK

WDCON (A7H)

SHADOW REGISTER

PRESCALER

002aaa905

8-BIT DOWN

COUNTER

WDL (C1H)

watchdog

oscillator

PCLK

÷

32

MOV WFEED1, #0A5H

MOV WFEED2, #05AH

reset

(1)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P89LPC932A1FA | 8-Bit Microcontroller with accelerated two-clock 80C51 core 8kB 3V byte-erasable flash with 512-byte data EEPROM |

| P8N18 | N-CHANNEL LOGIC LEVEL POWER FIELD EFFECT TRANSISTORS |

| P8XC557E8 | 8 BIT MICROCONTROLLER |

| P87C557E8 | 8 BIT MICROCONTROLLER |

| P8XC591 | HiRel FPGA, Low-Power 1.0?? CMOS Technology |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P89LPC933 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller with accelerated two-clock 80C51 core 4 kB/8 kB/16 kB 3 V byte-erasable flash with 8-bit ADCs |

| P89LPC9331 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller with accelerated two-clock 80C51 core, 4 kB/8 kB/16 kB 3 V byte-erasable flash with 8-bit ADCs |

| P89LPC9331_11 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller with accelerated two-clock 80C51 core, 4 kB/8 kB/16 kB 3 V byte-erasable |

| P89LPC9331FDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller with accelerated two-clock 80C51 core, 4 kB/8 kB/16 kB 3 V byte-erasable flash with 8-bit ADCs |

| P89LPC9331FDH,512 | 功能描述:8位微控制器 -MCU IC 80C51 MCU FLASH 4K RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。