- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369943 > P83C552IFB (NXP Semiconductors N.V.) Single-chip 8-bit microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | P83C552IFB |

| 廠(chǎng)商: | NXP Semiconductors N.V. |

| 英文描述: | Single-chip 8-bit microcontroller |

| 中文描述: | 單芯片8位微控制器 |

| 文件頁(yè)數(shù): | 13/23頁(yè) |

| 文件大小: | 185K |

| 代理商: | P83C552IFB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)

Philips Semiconductors

Product data

80C552/83C552

Single-chip 8-bit microcontroller with 10-bit A/D,

capture/compare timer, high-speed outputs, PWM

2002 Sep 03

13

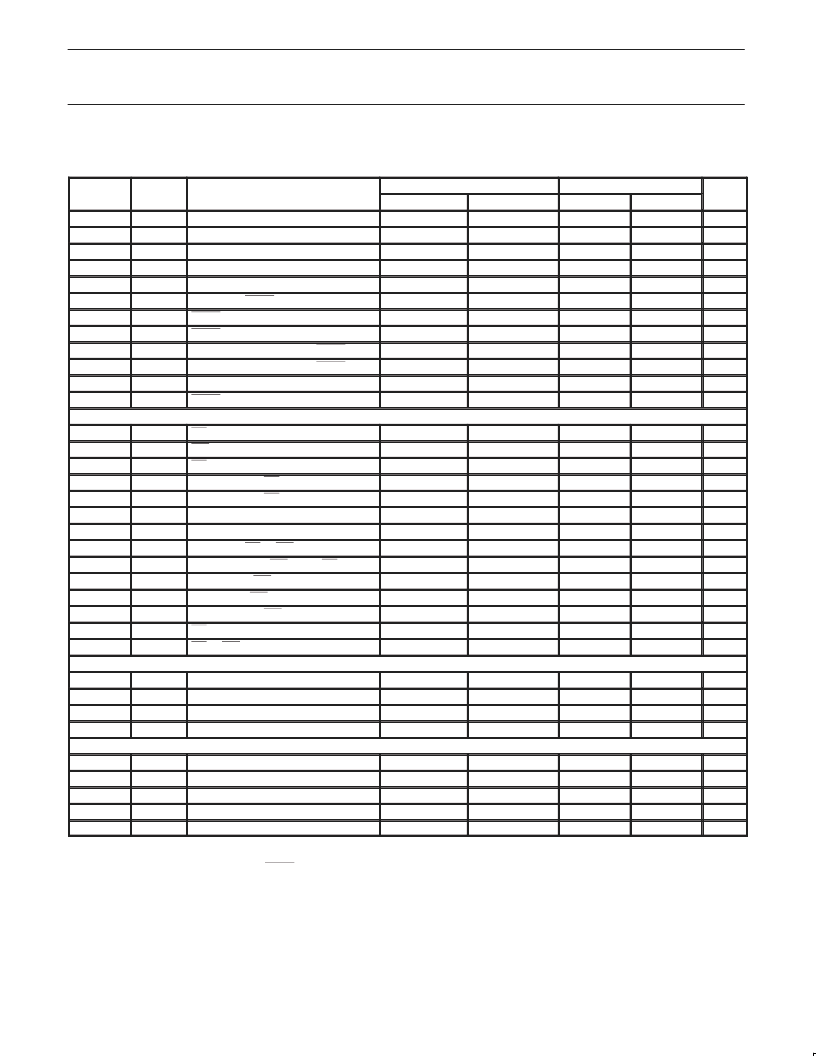

AC ELECTRICAL CHARACTERISTICS

1, 2

16 MHz version

16 MHz CLOCK

MIN

VARIABLE CLOCK

MIN

3.5

2t

CLCL

–40

t

CLCL

–55

t

CLCL

–35

SYMBOL

1/t

CLCL

t

LHLL

t

AVLL

t

LLAX

t

LLIV

t

LLPL

t

PLPH

t

PLIV

t

PXIX

t

PXIZ

t

AVIV

t

PLAZ

Data Memory

t

RLRH

t

WLWH

t

RLDV

t

RHDX

t

RHDZ

t

LLDV

t

AVDV

t

LLWL

t

AVWL

t

QVWX

t

DW

t

WHQX

t

RLAZ

t

WHLH

External Clock

t

CHCX

t

CLCX

t

CLCH

t

CHCL

Serial Timing – Shift Register Mode

4

(Test Conditions: T

amb

= 0

°

C to +70

°

C; V

SS

= 0 V; Load Capacitance = 80 pF)

t

XLXL

6

Serial port clock cycle time

t

QVXH

6

Output data setup to clock rising edge

t

XHQX

6

Output data hold after clock rising edge

t

XHDX

6

Input data hold after clock rising edge

t

XHDV

6

Clock rising edge to input data valid

NOTES:

1. Parameters are valid over operating temperature range unless otherwise specified.

2. Load capacitance for port 0, ALE, and PSEN = 100 pF, load capacitance for all other outputs = 80 pF.

3. t

CLCL

= 1/f

OSC

= one oscillator clock period.

t

CLCL

= 83.3ns at f

OSC

= 12 MHz.

t

CLCL

= 62.5ns at f

OSC

= 16 MHz.

4. These values are characterized but not 100% production tested.

FIGURE

2

2

2

2

2

2

2

2

2

2

2

2

PARAMETER

MAX

MAX

16

UNIT

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Oscillator frequency

ALE pulse width

Address valid to ALE low

Address hold after ALE low

ALE low to valid instruction in

ALE low to PSEN low

PSEN pulse width

PSEN low to valid instruction in

Input instruction hold after PSEN

Input instruction float after PSEN

Address to valid instruction in

PSEN low to address float

85

8

28

150

4t

CLCL

–100

23

143

t

CLCL

–40

3t

CLCL

–45

83

3t

CLCL

–105

0

0

38

208

10

t

CLCL

–25

5t

CLCL

–105

10

3

4

3

3

3

3

3

RD pulse width

WR pulse width

RD low to valid data in

Data hold after RD

Data float after RD

ALE low to valid data in

Address to valid data in

ALE low to RD or WR low

Address valid to WR low or RD low

Data valid to WR transition

Data before WR

Data hold after WR

RD low to address float

RD or WR high to ALE high

275

275

6t

CLCL

–100

6t

CLCL

–100

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

148

5t

CLCL

–165

0

0

55

350

398

238

2t

CLCL

–70

8t

CLCL

–150

9t

CLCL

–165

3t

CLCL

+50

3, 4

3, 4

4

4

4

3

3, 4

138

120

3

288

13

3t

CLCL

–50

4t

CLCL

–130

t

CLCL

–60

7t

CLCL

–150

t

CLCL

–50

0

0

23

103

t

CLCL

–40

t

CLCL

+40

5

5

5

5

High time

4

Low time

4

Rise time

4

Fall time

4

20

20

20

20

ns

ns

ns

ns

20

20

20

20

0.75

492

8

0

12t

CLCL

10t

CLCL

–133

2t

CLCL

–117

0

μ

s

ns

ns

ns

ns

492

10t

CLCL

–133

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P80C552KBA | Single-chip 8-bit microcontroller |

| P83C552KBA | Single-chip 8-bit microcontroller |

| P83C552EBA | Single-chip 8-bit microcontroller |

| P83C552EBB | Single-chip 8-bit microcontroller |

| P83C552EFB | Single-chip 8-bit microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P83C552IFB/XXX | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Single-chip 8-bit microcontroller |

| P83C552KBA | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Single-chip 8-bit microcontroller |

| P83C552KBA/XXX | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:MICROCONTROLLER|8-BIT|8051 CPU|CMOS|LDCC|68PIN|PLASTIC |

| P83C552KBB | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Single-chip 8-bit microcontroller |

| P83C552KBB/XXX | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:MICROCONTROLLER|8-BIT|8051 CPU|CMOS|QFP|80PIN|PLASTIC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。