- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄369940 > P3Z22V10IBA (NXP SEMICONDUCTORS) 3V zero power, TotalCMOS, universal PLD device PDF資料下載

參數(shù)資料

| 型號(hào): | P3Z22V10IBA |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | PLD |

| 英文描述: | 3V zero power, TotalCMOS, universal PLD device |

| 中文描述: | EE PLD, 15 ns, PQCC28 |

| 封裝: | PEDESTAL, PLASTIC, SOT-261-3, LCC-28 |

| 文件頁(yè)數(shù): | 6/16頁(yè) |

| 文件大?。?/td> | 191K |

| 代理商: | P3Z22V10IBA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

Philips Semiconductors

Product specification

P3Z22V10

3V zero power, TotalCMOS

, universal PLD device

1997 Jul 18

6

F

0

1

1

0

0

1

0

0

1

CLK

1

AR

SP

S

1

S

0

S

1

S

0

OUTPUT CONFIGURATION

0 = Unprogrammed fuse

1 = Programmed fuse

D

Q

Q

0

0

1

1

0

1

0

1

Registered/Active-LOW/Macrocell feedback

Registered/Active-HIGH/Macrocell feedback

Combinatorial/Active-LOW/Pin feedback

Combinatorial/Active-HIGH/Pin feedback

SP00484

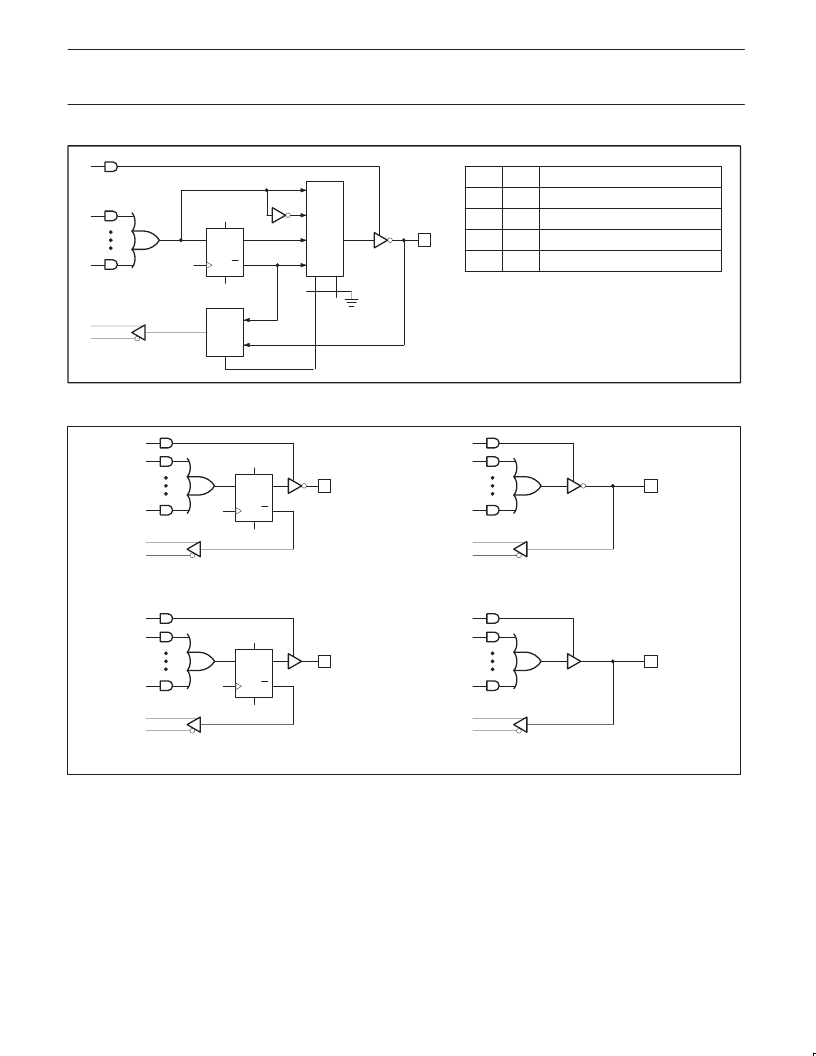

Figure 2.

Output Macro Cell Logic Diagram

F

CLK

AR

SP

S

0

= 0

S

1

= 0

D

Q

Q

a. Registered/Active-LOW

F

CLK

AR

SP

S

0

= 1

S

1

= 0

D

Q

Q

b. Registered/Active-HIGH

F

S

0

= 0

S

1

= 1

c. Combinatorial/Active-LOW

d. Combinatorial/Active-HIGH

F

S

0

= 1

S

1

= 1

SP00376

Figure 3.

Output Macro Cell Configurations

Programmable I/O Macrocell

The output macrocell provides complete control over the

architecture of each output. the ability to configure each output

independently permits users to tailor the configuration of the

P3Z22V10 to the precise requirements of their designs.

Macrocell Architecture

Each I/O macrocell, as shown in Figure 2, consists of a D-type

flip-flop and two signal-select multiplexers. The configuration of each

macrocell of the P3Z22V10 is determined by the two EEPROM bits

controlling these multiplexers. These bits determine output polarity,

and output type (registered or non-registered). Equivalent circuits for

the macrocell configurations are illustrated in Figure 3.

Output type

The signal from the OR array can be fed directly to the output pin

(combinatorial function) or latched in the D-type flip-flop (registered

function). The D-type flip-flop latches data on the rising edge of the

clock and is controlled by the global preset and clear terms. When

the synchronous preset term is satisfied, the Q output of the register

will be set HIGH at the next rising edge of the clock input. Satisfying

the asynchronous clear term will set Q LOW, regardless of the clock

state. If both terms are satisfied simultaneously, the clear will

override the preset.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P3Z22V10IBD | 3V zero power, TotalCMOS, universal PLD device |

| P4010 | HIGH RELIABILITY PHOTOCOUPLER |

| P4010A | HIGH RELIABILITY PHOTOCOUPLER |

| P4010B | HIGH RELIABILITY PHOTOCOUPLER |

| P4010C | HIGH RELIABILITY PHOTOCOUPLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P3Z22V10IBD | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3V zero power, TotalCMOS, universal PLD device |

| P3Z22V10IBDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3V zero power, TotalCMOS, universal PLD device |

| P3Z7AAT800W | 制造商:POWEREX 制造商全稱:Powerex Power Semiconductors 功能描述:Phase Control Modules (345-800 Amperes/400-3000 Volts) |

| P3Z7AAT800W22 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:THYRISTOR MODULE|SCR DOUBLER|2.2KV V(RRM)|300A I(T) |

| P3Z7AAT800W24 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:THYRISTOR MODULE|SCR DOUBLER|2.4KV V(RRM)|300A I(T) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。