- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361076 > NBC12429 (ON SEMICONDUCTOR) 3.3V/5V Programmable PLL Synthesized Clock Generator(3.3V/5V可編程PLL合成時鐘發(fā)生器) PDF資料下載

參數(shù)資料

| 型號: | NBC12429 |

| 廠商: | ON SEMICONDUCTOR |

| 英文描述: | 3.3V/5V Programmable PLL Synthesized Clock Generator(3.3V/5V可編程PLL合成時鐘發(fā)生器) |

| 中文描述: | 3.3V/5V的可編程鎖相環(huán)路合成時鐘發(fā)生器(3.3V/5V的可編程PLL頻率合成時鐘發(fā)生器) |

| 文件頁數(shù): | 8/20頁 |

| 文件大小: | 351K |

| 代理商: | NBC12429 |

NBC12429, NBC12429A

http://onsemi.com

8

FUNCTIONAL DESCRIPTION

The internal oscillator uses the external quartz crystal as

the basis of its frequency reference. The output of the

referenceoscillatorisdividedby16beforebeingsenttothe

phase detector. With a 16 MHz crystal, this provides a

reference frequency of 1 MHz. Although this data sheet

illustrates functionality only for a 16 MHz crystal, Table 9,

any crystal in the 10 MHz -- 20 MHz range can be used,

Table 11.

The VCO within the PLL operates over a range of 200 to

400 MHz.Itsoutputisscaledbyadividerthatisconfigured

by either the serial or parallel interfaces. The output of this

loop divider is also applied to the phase detector.

The phase detector and the loop filter force the VCO

output frequency to be M times the reference frequency by

adjusting the VCO control voltage. Note that for some

values of M (either too high or too low), the PLL will not

achieve loop lock.

The output of the VCO is also passed through an output

divider before being sent to the PECL output driver. This

output divider (N divider) is configured through either the

serial or the parallel interfaces and can provide one of four

division ratios (1, 2, 4, or 8). This divider extends the

performance of the part while providing a 50% duty cycle.

The output driver is driven differentially from the output

dividerandiscapableofdrivingapairoftransmissionlines

terminatedinto50

Ω

toV

CC

-- 2.0 V.Thepositivereference

fortheoutputdriverandtheinternallogicisseparatedfrom

the power supply for the PLL to minimize noise induced

jitter.

The configuration logic has two sections: serial and

parallel.The parallelinterface usesthe valuesat theM[8:0]

and N[1:0] inputs to configure the internal counters.

Normally upon system reset, the P_LOAD input is held

LOW until sometime after power becomes valid. On the

LOW--to--HIGH transition of P_LOAD, the parallel inputs

are captured. The parallel interface has priority over the

serialinterface.Internalpullupresistorsareprovidedonthe

M[8:0] and N[1:0] inputs to reduce component count in the

application of the chip.

The serial interface logic is implemented with a fourteen

bit shift register scheme. The register shifts once per rising

edgeoftheS_CLOCKinput.TheserialinputS_DATAmust

meet setup and hold timing as specified in the AC

Characteristics section of this document. With P_LOAD

heldhigh,theconfigurationlatcheswillcapturethevalueof

the shift register on the HIGH--to--LOW edge of the

S_LOAD input. See the programming section for more

information.

TheTESToutputreflectsvariousinternalnodevaluesand

is controlled by the T[2:0] bits in the serial data stream.See

the programming section for more information.

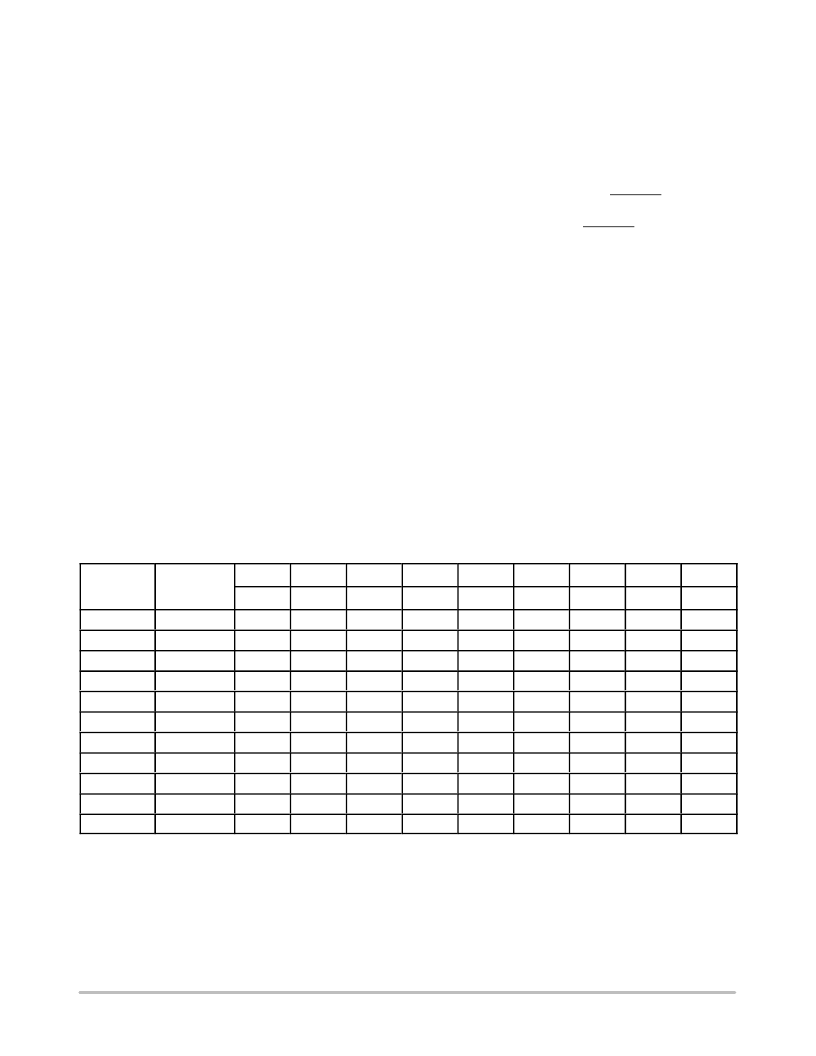

Table 9. Programming VCO Frequency Function Table with 16 MHz Crystal

VCO

Frequency

(MHz)

M

Count

Divisor

256

128

64

32

16

8

4

2

1

M8

M7

M6

M5

M4

M3

M2

M1

M0

200

200

0

1

1

0

0

1

0

0

0

201

201

0

1

1

0

0

1

0

0

1

202

202

0

1

1

0

0

1

0

1

0

203

203

0

1

1

0

0

1

0

1

1

397

397

1

1

0

0

0

1

1

0

1

398

398

1

1

0

0

0

1

1

1

0

399

399

1

1

0

0

0

1

1

1

1

400

400

1

1

0

0

1

0

0

0

0

相關PDF資料 |

PDF描述 |

|---|---|

| NBC12429A | 3.3V/5V Programmable PLL Synthesized Clock Generator(3.3V/5V可編程PLL合成時鐘發(fā)生器) |

| NBC12430 | 3.3V/5V Programmable PLL Synthesized Clock Generator(3.3V/5V可編程PLL合成時鐘發(fā)生器) |

| NBC12430A | 3.3V/5V Programmable PLL Synthesized Clock Generator(3.3V/5V可編程PLL合成時鐘發(fā)生器) |

| NBC12439A | 3.3V/5V Programmable PLL Synthesized Clock Generator(3.3V/5V可編程PLL合成時鐘發(fā)生器) |

| NBC12439 | 3.3V/5V Programmable PLL Synthesized Clock Generator(3.3V/5V可編程PLL合成時鐘發(fā)生器) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| NBC12429/D | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:3.3 V/5 V Programmable PLL Synthesized Clock Generator (25 to 400 MHz) |

| NBC12429_07 | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:3.3V/5V Programmable PLL Synthesized Clock Generator |

| NBC12429A | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:3.3V/5V Programmable PLL Synthesized Clock Generator |

| NBC12429AFA | 功能描述:鎖相環(huán) - PLL 3.3V/5V Programmable RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| NBC12429AFAG | 功能描述:鎖相環(huán) - PLL 3.3V/5V Programmable PLL Clock Generator RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。