- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45594 > MUPA64K16-15TJI SPECIALTY MICROPROCESSOR CIRCUIT, PQFP128 PDF資料下載

參數(shù)資料

| 型號: | MUPA64K16-15TJI |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PQFP128 |

| 封裝: | LQFP-128 |

| 文件頁數(shù): | 3/19頁 |

| 文件大小: | 380K |

| 代理商: | MUPA64K16-15TJI |

MUPA64K16 Alto Priority Queue Scheduler

MUSIC Semiconductors Confidential

11

Rev 0.3 Draft

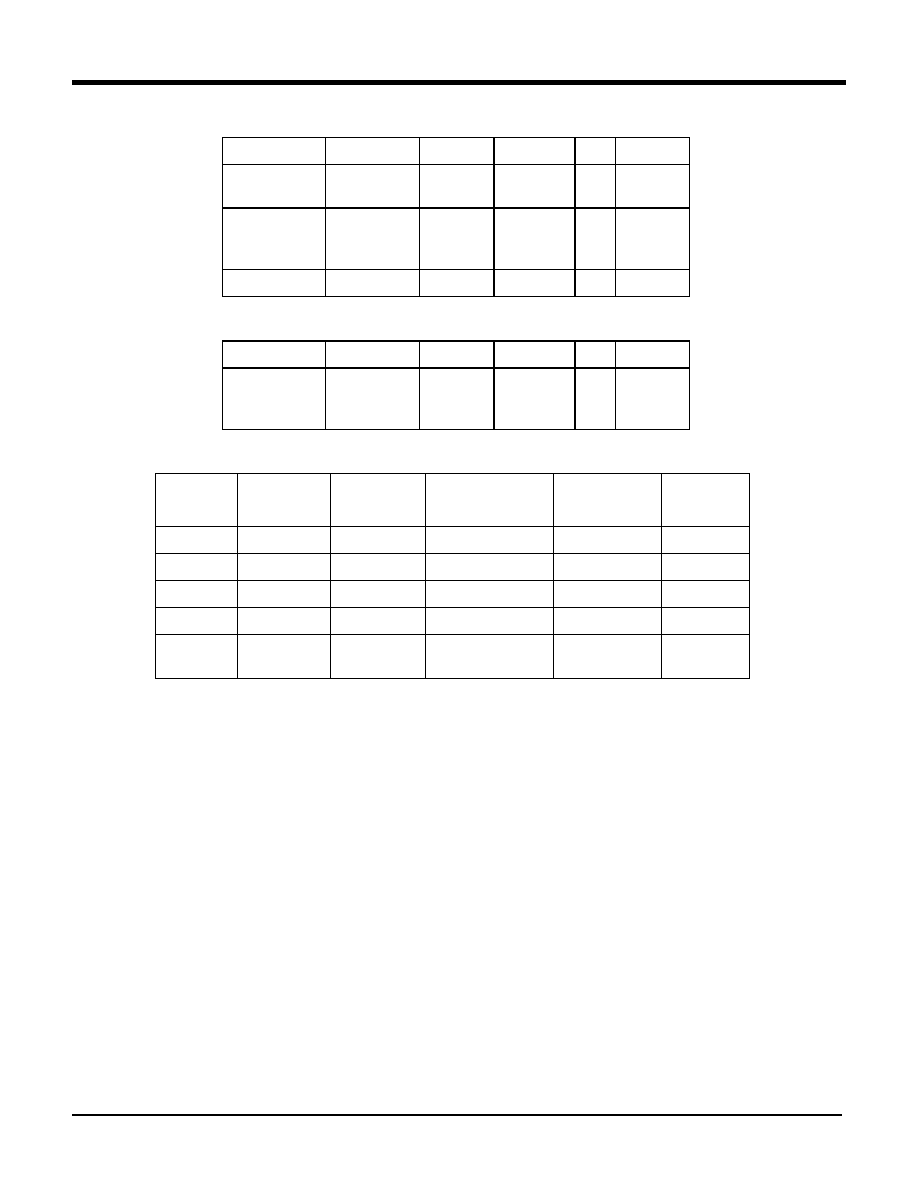

Table 10: UID Get Operation

Operation

Instruction

OP[2:0]

REG[2:0]

/W

PQ[3:0]

Start

UID

Get

UID Get

5

N/A

1

N

Wait for UID

Get

to

complete

Read UGR

Noop

0

5

1

N

Table 11: UID Put Operation

Operation

Instruction

OP[2:0]

REG[2:0]

/W

PQ[3:0]

Write UPR,

Start UID

Put

UID Put

6

0

N

Table 12: Size and Wrap Registers

MR[2:0]

Number of

Queues

Number of

Size

Registers

Number of

Wrap registers

Width of

Size register

PQ Lines

used

000

1

16 bits

none

001

2

15 bits

PQ[0]

010

4

14 bits

PQ[1,0]

011

8

13 bits

PQ[2:0]

100, 101,

110, 111

16

12 bits

PQ[3:0]

Size and Wrap register bank and instruction

decode

The SWM module contains: Instruction decode and

write logic for 16 SR (Size) registers and 16 WR

(Wrap) registers. Priority queue can be configured

with use of PQ[3:0] inputs and mode register bits

MR[2:0]. Table 12 shows the relationship between

the PQ[3:0], MR[2:0] and number of queues.

Decode logic for queue operation instructions: insert,

extract, both, peek, Ram Write, Ram Read. Decode

logic for instruction that reads size and wrap register

contents pointed to by PQ inputs.

Size register contents are cleared when a write is

detected either for mode register or for size register.

Size register contents pointed to by PQ and mode

register are increased or decreased by one if an

instruction in execution is insert or extract.

Wrap register contents are cleared when a write is

detected for mode register. When a write is detected

for wrap register, using PQ value and mode register

contents, appropriate wrap register is updated from

DQ input.

When an instruction that operates on queue (insert,

extract, peek, both) is detected, PQ, opcode, size

register, wrap register, IKR and IDR are stored in a

buffer. Upon detection of completion of previously

issued

queue

instruction,

the

contents

are

transferred to the priority queue for execution of the

queue instruction. The buffer is now ready to accept

one additional queue instruction from external

interface.

If it is not required to read the Size Register all the

time, it can be tracked in ASIC.

The following is an example of a complex set of

pipelined instructions. The basic sequence is six

instructions, but they're interleaved to achieve

optimal pipelining.

相關PDF資料 |

PDF描述 |

|---|---|

| MUR1005FCT | 10 A, 50 V, SILICON, RECTIFIER DIODE, TO-220AB |

| MUR1020FCT | 10 A, 200 V, SILICON, RECTIFIER DIODE, TO-220AB |

| MUR1030FCT | 10 A, 300 V, SILICON, RECTIFIER DIODE, TO-220AB |

| MUR1040FCT | 10 A, 400 V, SILICON, RECTIFIER DIODE, TO-220AB |

| MUR1005FCTP | 10 A, 50 V, SILICON, RECTIFIER DIODE, TO-220AB |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| mur | 制造商:Datak Corporation 功能描述: |

| MUR 120G | 制造商:ON Semiconductor 功能描述:Bulk |

| MUR 3 | 制造商:Crouzet 功能描述:Bulk |

| MUR 3020WTPBF | 制造商:Vishay 功能描述:Bulk |

| MUR 4100EG | 制造商:ON Semiconductor 功能描述:Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。