- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376207 > MTV003N (Electronic Theatre Controls, Inc.) Microprocessor Compatible Monitor Controller PDF資料下載

參數(shù)資料

| 型號(hào): | MTV003N |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Microprocessor Compatible Monitor Controller |

| 中文描述: | 微處理器兼容顯示器控制器 |

| 文件頁(yè)數(shù): | 4/13頁(yè) |

| 文件大小: | 224K |

| 代理商: | MTV003N |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)

MYSON

TECHNOLOGY

MTV003N

(MTV003)

MTV003 Revision 2.3 07/01/1998

4/13

for each converter by setting the corresponding register.

3.3 SYNC Processor

The sync processor contains the following functions: polarity detection, presence detection, H-Freq counter,

V-Freq counter and sync signal separation for input SYNC sources (HS and VS). It can be programmed to

change the detected polarity status and output polarity of SYNC pins (HBLANK and VBLANK) by using the

command interface. The timing diagrams of sync processing are shown as Fig. 2 in section 8.0. The internal

SYNC signals (Hsync and Vsync) are extracted from different sources according to the following modes of

operation.

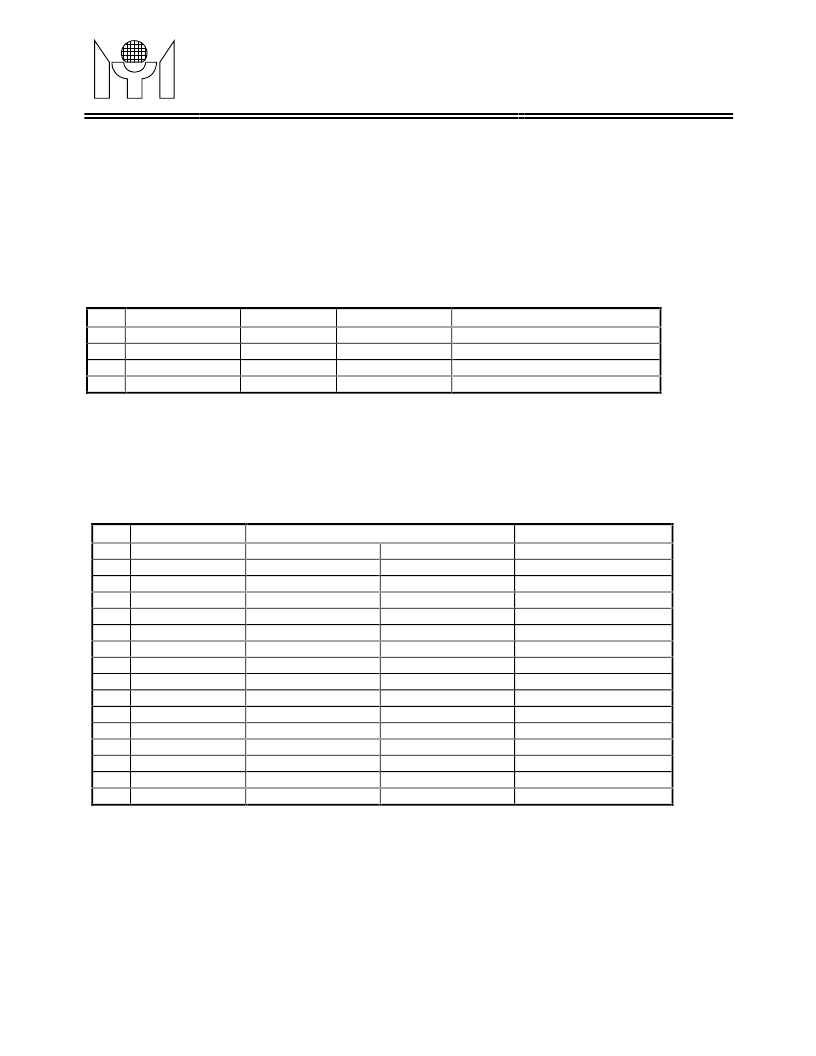

Mode

VS

HS

Comment

1

2

3

4

Separate(H+V)

Composite(H/V)

Suspend

Off

present

not present

present

not present

present

present

not present

not present

HS = H or H/V sync

HS= H/V sync

-

-

3.4 H-Freq Table

After the "start H-Freq count" command is issued over 10 ms (for 15.7KHz) and HCFF(H-Freq Count Finished

Flag) is set

High,

the H-Freq output (HF9 - HF0) is valid. The output value of H-Freq is calculated using the

following formula:

output value = [(1/fHfreq(KHz)) x 64 x 4000] / 16

H-Freq(KHz)

15.7

18.7

21.8

30

31.5

33.5

35.5

36.8

38

40

48

50

57

60

64

100

Output value hexadecimal 11 bits decimal

3FB

357

2DD

215

1FB

1DD

1C2

1B2

1A5

190

14D

140

118

10A

0FA

0A0

Tolerance (%)

0.0981354

0.1169591

0.1364256

0.1876172

0.1972386

0.2096436

0.2222222

0.2304147

0.2375297

0.2500000

0.3003003

0.3125000

0.3571428

0.3759398

0.4000000

0.6250000

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1019

855

733

533

507

477

450

434

421

400

333

320

280

266

250

160

3.5 V-Freq Table

After the "start V-Freq count" command is issued over 120 ms (for 50HZ) and VCFF (V-Freq Count Finish Flag)

is set

High,

the V-Freq output (VF8 - VF0) is valid. The output value of V-Freq is calculated according to the

following formula:

output value = [(4/fVfreq(Hz)) x 4000000] / (64 x 16)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MTV004 | On-Screen Display Shrink Version |

| MTV012A | 8051 Embedded CRT Monitor Controller Mask Version |

| MTV012E | 8051 Embedded CRT Monitor Controller OTP Version |

| MTV018 | IC TXRX PHY 10/100 3.3V 48LQFP |

| MTV021 | Enhanced Super On-Screen Display |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MTV004 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:On-Screen Display Shrink Version |

| MTV012A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8051 Embedded CRT Monitor Controller Mask Version |

| MTV012E | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8051 Embedded CRT Monitor Controller OTP Version |

| MTV016 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced On-Screen-Display Controller |

| MTV016N-10 | 制造商:Myson Century Inc 功能描述:IC, PDIP16 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。