- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359235 > MT9171AP (Mitel Networks Corporation) ISO2-CMOS ST-BUS⑩ FAMILY Digital Subscriber Interface Circuit Digital Network Interface Circuit PDF資料下載

參數(shù)資料

| 型號(hào): | MT9171AP |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | ISO2-CMOS ST-BUS⑩ FAMILY Digital Subscriber Interface Circuit Digital Network Interface Circuit |

| 中文描述: | ISO2 -意法半導(dǎo)體的CMOS總線⑩家庭數(shù)字用戶接口電路的數(shù)字網(wǎng)絡(luò)接口電路 |

| 文件頁數(shù): | 15/25頁 |

| 文件大?。?/td> | 401K |

| 代理商: | MT9171AP |

Advance Information

MT9171/72

9-129

Applications

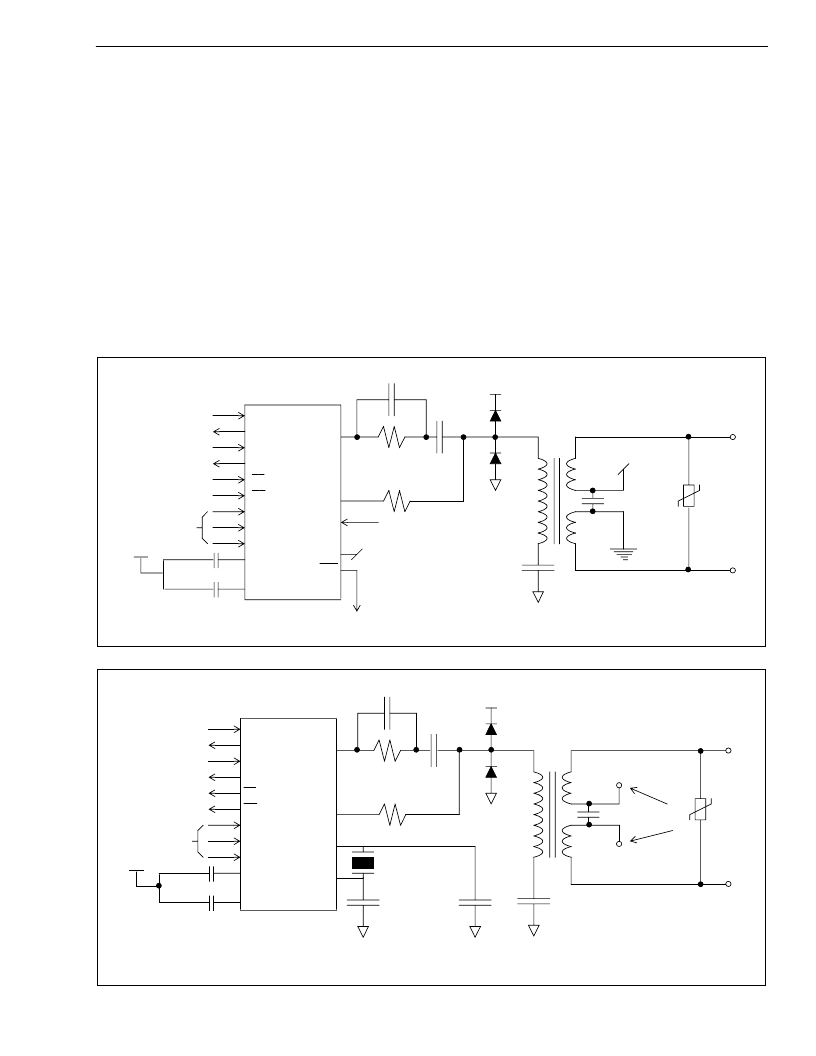

Typical connection diagrams are shown in Figures 13

and 14 for the DN mode as a MASTER and SLAVE,

respectively. L

OUT

is connected to the coupling

transformer through a resistor R2 and capacitors C2

and C2’ to match the line characteristic impedance.

Suggested values of R2, C2 and C2’ for 80 and 160

kbit/s operation are provided in Figures 13 and 14.

Overvoltage protection is provided by R1, D1 and

D2. C1 is present to properly bias the received line

signal for the L

IN

input. A 2:1 coupling transformer is

used to couple to the line with a secondary center

tap for optional phantom power feed. Varistors have

been shown for surge protection against such things

as lightning strikes.

If the scramblers power up with all zeros in them,

they are not capable of randomizing all-zeros data

sequence. This increases the correlation between

the transmit and receive data which may cause loss

of convergence in the echo canceller and high bit

error rates.

In DN mode the insertion of the SYNC pattern will

provide enough pseudo-random activity to maintain

convergence. In MOD mode the SYNC pattern is not

inserted. For this reason, at least on ”1” must be fed

into the DNIC on power up to ensure that the

scramblers will randomize any subsequent all-zeros

sequence.

Figure 13 - Typical Connection Diagram - MAS/DN Mode, 160 kbit/s

Figure 14 - Typical Connection Diagram - SLV/DN Mode, 160 kbit/s

DV Port ST-BUS

CD Port ST-BUS

Master Clocks

Mode Select

Lines

{

{

{

+5V

0.33

μ

F

0.33

μ

F

DSTi

DSTo

CDSTi

CDSTo

F0

C4

MS0

MS1

MS2

V

Ref

V

Bias

L

OUT

L

IN

OSC1

OSC2

F0o

NC

D.C. coupled,

Frequency locked

10.24 MHz clock.

Refer to AC Electrical

R2 = 390

R1 = 47

C2’ = 1.5 nF

C2 = 22 nF

+5V

D1 = D2 = MUR405

D2

2 : 1

1.0

μ

F

Line Feed

Voltage

For 80 kbit/s: C2’ = 3.3 nF

C1 = 0.33

μ

F

68 Volts

(Typ)

2.5 Joules

0.02 Watt

Note:

Low leakage diodes (1 & 2) are required so

that the DC voltage at L

IN

≈

V

Bias

To Next DNIC

MT9171/72

Characteristics

Clock Timing

DN Mode.

DV Port ST-BUS

CD Port ST-BUS

Master Clocks

Mode Select

Lines

+5V

0.33

μ

F

0.33

μ

F

DSTi

DSTo

CDSTi

CDSTo

F0

C4

MS0

MS1

MS2

V

Ref

V

Bias

L

OUT

L

IN

OSC1

OSC2

R2 = 390

R1 = 47

C2’ = 1.5 nF

C2 = 22 nF

+5V

D1 = D2 = MUR405

D2

2:1

{

{

{

1.0

μ

F

For 80 kbit/s: C2’ = 3.3 nF

C1 = 0.33

μ

F

68 Volts

(Typ)

2.5 Joules

0.02 Watt

Note:

Low leakage diodes (1 & 2) are required so

that the DC voltage at L

IN

≈

V

Bias

10.24 MHz XTAL

C3=33pF=C4

Supply

MT9171/72

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9173AE1 | Digital Subscriber Interface Circuit with RxSB Digital Network Interface Circuit with RxSB |

| MT9196AE1 | Integrated Digital Phone Circuit (IDPC) |

| MT92220 | 1023 Channel Voice Over IP/AAL2 Processor |

| MT9300B | Multi-Channel Voice Echo Canceller |

| MT9300BL | Multi-Channel Voice Echo Canceller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9171AP1 | 制造商:Microsemi Corporation 功能描述:PB FREE DNIC 1.5UM - Rail/Tube 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE DNIC 1.5UM - Rail/Tube |

| MT9171APR | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Digital Subscriber Interface Circuit Digital Network Interface Circuit |

| MT9171APR1 | 制造商:Microsemi Corporation 功能描述:PB FREE 1.5UM DNIC - Tape and Reel 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE 1.5UM DNIC - Tape and Reel |

| MT9172 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Digital Subscriber Interface Circuit Digital Network Interface Circuit |

| MT9172AC | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO2-CMOS ST-BUS⑩ FAMILY Digital Subscriber Interface Circuit Digital Network Interface Circuit |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。