- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359235 > MT9171 (Zarlink Semiconductor Inc.) ISO2-CMOS ST-BUS FAMILY PDF資料下載

參數(shù)資料

| 型號: | MT9171 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | ISO2-CMOS ST-BUS FAMILY |

| 中文描述: | ISO2 -意法半導(dǎo)體的CMOS總線家庭 |

| 文件頁數(shù): | 17/25頁 |

| 文件大?。?/td> | 401K |

| 代理商: | MT9171 |

Advance Information

MT9171/72

9-131

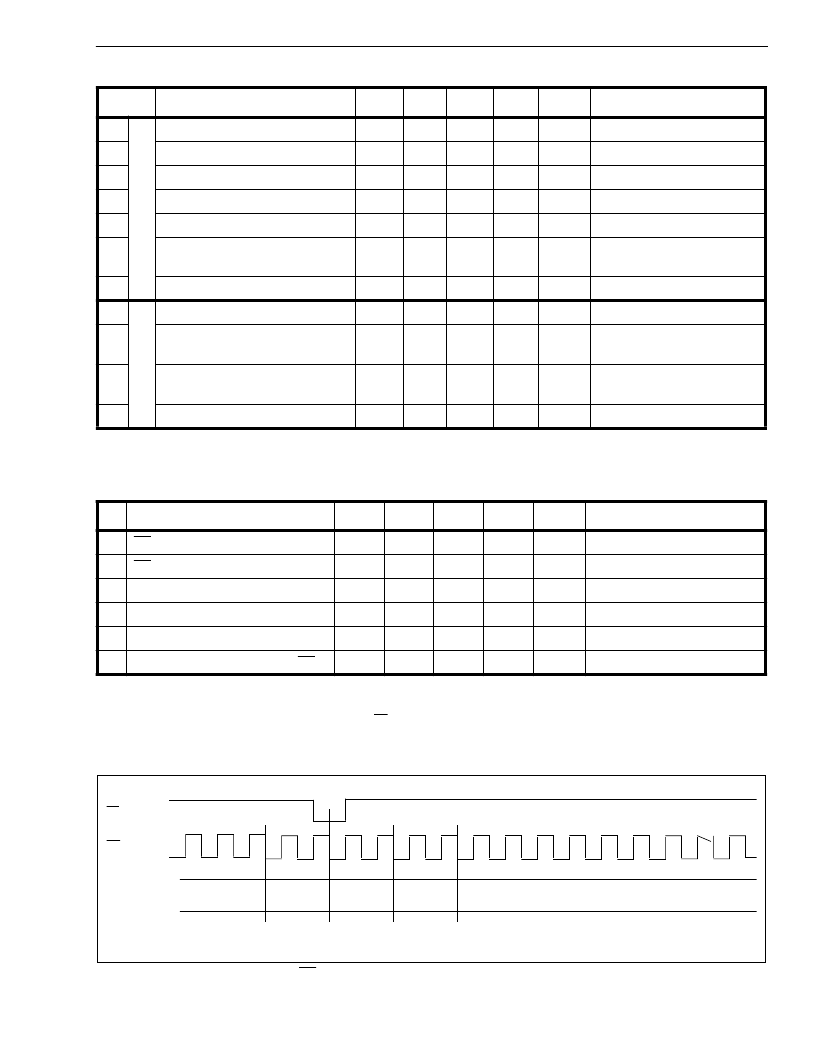

Timing is over recommended temperature & power supply voltages.

* Typical figures are at 25

°

C and are for design aid only: not guaranteed and not subject to production testing.

Duty cycle is measured at V

DD

/2 volts.

.

Timing is over recommended temperature & power supply voltages.

* Typical figures are at 25

°

C and are for design aid only: not guaranteed and not subject to production testing.

Notes:

1)

When operating as a SLAVE the C4 clock has a 40% duty cycle.

2)

When operating in MAS/DN Mode, the C4 and Oscillator clocks must be externally frequency-locked (i.e.,

F

C

=2.5xf

C4

). The relative phase between these two clocks (

Φ

in Fig. 17) is not critical and may vary from

0 ns to t

C4P

. However, the relative jitter must be less than J

C

(see Figure 17).

Figure 15 - C4 Clock & Frame Pulse Alignment for ST-BUS Streams

AC Electrical Characteristics

- Voltages are with respect to ground (V

SS

) unless otherwise stated.

Characteristics

Sym

Min

Typ*

Max

Units

Test Conditions

1

I

N

P

U

T

S

Input Voltage

(L

IN)

(L

IN

)

V

IN

Z

IN

f

C

T

C

DC

C

DC

C

5.0

V

pp

k

2

Input Impedance

20

f

Baud

=160 kHz

3

Crystal/Clock Frequency

10.24

MHz

4

Crystal/Clock Tolerance

-100

0

+100

ppm

5a

Crystal/Clock Duty Cycle

40

50

60

%

Normal temp. & V

DD

Recommended at max./

min. temp. & V

DD

From OSC1 & OSC2 to V

SS

.

5b

Crystal/Clock Duty Cycle

45

50

55

%

6

Crystal/Clock Loading

C

L

C

o

R

Lout

33

50

pF

7

O

U

T

P

U

T

S

Output Capacitance

(L

OUT

)

(L

OUT

)

8

pF

8

Load Resistance

(V

Bias

, V

Ref

)

500

100

k

9

Load Capacitance

(L

OUT

)

(V

Bias

, V

Ref

)

C

Lout

0.1

20

pF

μ

F

Capacitance to V

Bias

.

10

Output Voltage

(L

OUT

)

V

o

3.2

4.3

4.6

V

pp

R

Lout

= 500

, C

Lout

= 20pF

AC Electrical Characteristics

- Clock Timing - DN Mode (Figures 16 & 17)

Characteristics

Sym

Min

Typ*

Max

Units

Test Conditions

1

C4 Clock Period

t

C4P

t

C4W

t

F0S

t

F0H

t

F0W

J

C

244

ns

2

C4 Clock Width High or Low

122

ns

In Master Mode - Note 1

3

Frame Pulse Setup Time

50

ns

4

Frame Pulse Hold Time

50

ns

5

Frame Pulse Width

244

ns

6

10.24 MHz Clock Jitter (wrt C4)

±

15

ns

Note 2

Channel 31

Bit 0

Channel 0

Bit 7

Channel 0

Bit 6

F0

C4

ST-BUS

BIT CELLS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9171AE | ISO2-CMOS ST-BUS FAMILY |

| MT9171AN | ISO2-CMOS ST-BUS FAMILY |

| MT9171AP | ISO2-CMOS ST-BUS FAMILY |

| MT9171 | ISO2-CMOS ST-BUS⑩ FAMILY Digital Subscriber Interface Circuit Digital Network Interface Circuit |

| MT9171AE | ISO2-CMOS ST-BUS⑩ FAMILY Digital Subscriber Interface Circuit Digital Network Interface Circuit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9171_06 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Digital Subscriber Interface Circuit Digital Network Interface Circuit |

| MT9171AE | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:ISO2-CMOS ST-BUS FAMILY |

| MT9171AE1 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Digital Subscriber Interface Circuit Digital Network Interface Circuit |

| MT9171AN | 制造商:Microsemi Corporation 功能描述: |

| MT9171AN1 | 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE DNIC 1.5UM - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。