- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359233 > MT8931CE (Mitel Networks Corporation) CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information PDF資料下載

參數(shù)資料

| 型號(hào): | MT8931CE |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information |

| 中文描述: | 意法半導(dǎo)體的CMOS總線⑩家庭用戶網(wǎng)絡(luò)接口電路的初步信息 |

| 文件頁數(shù): | 9/39頁 |

| 文件大小: | 833K |

| 代理商: | MT8931CE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

Data Sheet

MT8931C

9

with zeros in the B and D-channel and the

activation bit (A-bit) set to zero.

4) As soon as the TE synchronizes to Info2, it

responds with a valid S-Bus frame with data in

the B1, B2 and D-channel (Info3).

5) The NT will then transmit a valid frame with data

in the B1, B2 and D-channel. It will also set the

activation

bit

(A)

synchronization to Info3 is achieved.

to

binary

one

once

If the NT wishes to initiate the activation, steps 2 and

3 are ignored and the NT starts sending Info2. To

initiate a deactivation, either end begins to send

Info0 (Idle line).

D-channel Priority Mechanism

The SNIC contains a hardware priority mechanism

for D-channel contention resolution. All TEs

connected in a point-to-multipoint configuration are

allocated

the

D-channel

approach.

Allocation

accomplished by monitoring the D-echo channel

(E-bit) and incrementing the D-channel priority

counter with every consecutive one echoed back in

using

of

a

D-channel

systematic

the

is

the E bit. Any zero found on the D-echo channel will

reset the priority counter.

There are two classes of priority within the SNIC,

one user accessible and the other being strictly

internal. The user accessible priority selects the

class of operation and has precedence over the

internal priority. The latter (internal priority), will

select the level of priority within each class (i.e., the

internal priority is a subsection of the user accessible

priority). User accessible priority selects the terminal

count as 8/9 or 10/11 consecutive ones on the E-bit

(8 being high priority while 10 being low priority).

The internal priority selects the terminal between 8

or 9 for high class and 10 or 11 for low class. The

first terminal equipment to attain the E-bit priority

count will immediately take control of the D-channel

by sending the opening flag. If more than one

terminal has the same priority, all but one of them will

eventually detect a collision. The TEs that detect a

collision will immediately stop trans-mitting on the D-

channel, generate an interrupt through the Dcoll bit,

reset the DCack bit on the next frame pulse, and

restart the counting process. The remainder of the

packet in the Tx FIFO is ignored.

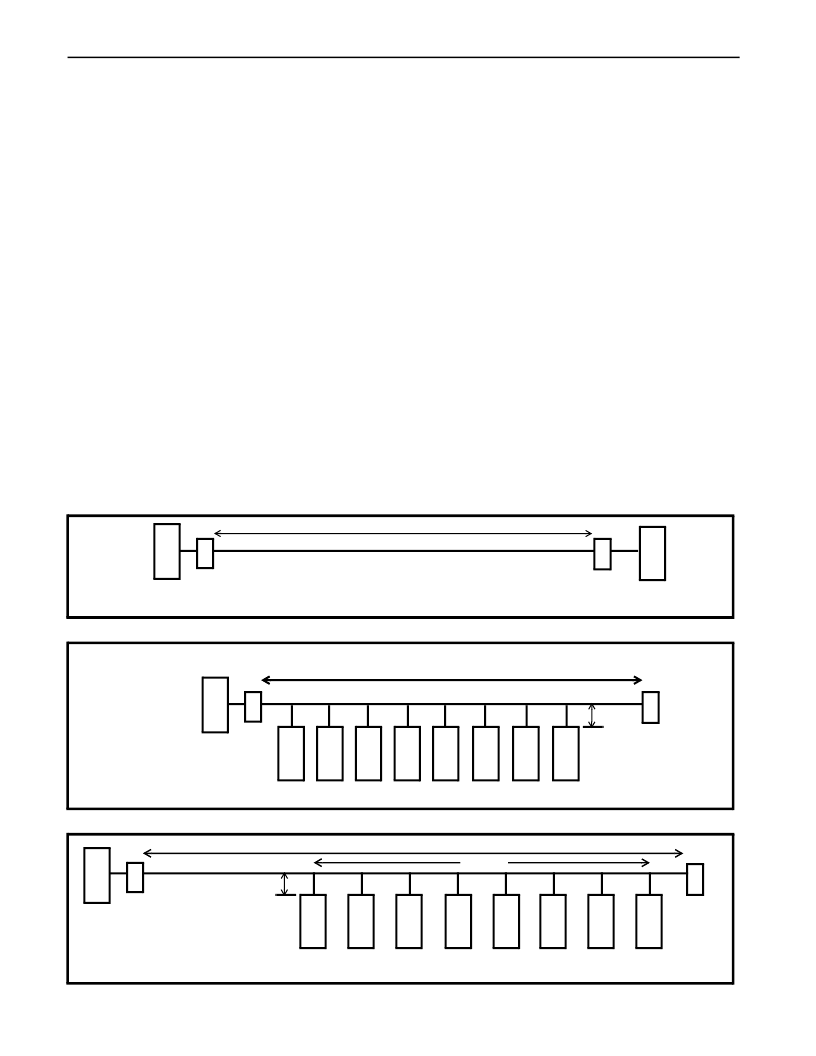

Figure 8 - Point-to-Point Configuration

Figure 9 - Short Passive Bus Configuration, up to 8 TEs can be supported

Figure 10 - Extended Passive Bus Configuration, up to 8 TEs can be supported

NT

TE

T

R

T

R

0 - 1 Km

NT is operating in adaptive timing

TR is the line termination resistor = 100

NT

TE

T

R

T

R

TE

TE

TE

TE

TE

TE

TE

100 m for 75

impedance cable and 200 m for 150

impedance cable

100 - 200 m

NT is operating in fixed timing

TR is the line termination resistor = 100

0 - 10 m

NT is operating in adaptive timing

TR is the line termination resistor = 100

TE

TE

TE

TE

TE

TE

TE

0 - 10 m

0-500 m

0-50 m

NT

T

R

T

R

TE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT8931C | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information |

| MT8931CC | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information |

| MT8931CP | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit |

| MT8941 | Advanced T1/CEPT Digital Trunk PLL |

| MT8941BE | Advanced T1/CEPT Digital Trunk PLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT8931CP | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Subscriber Network Interface Circuit |

| MT8940 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO-CMOS ST-BUS⑩ FAMILY T1/CEPT Digital Trunk PLL |

| MT8940-1 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO-CMOS ST-BUS⑩ FAMILY T1/CEPT Digital Trunk PLL |

| MT8940AC | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:T1/CEPT Digital Trunk PLL |

| MT8940AE | 制造商:MITEL 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。