- 您現(xiàn)在的位置:買賣IC網 > PDF目錄359233 > MT8931CE (Mitel Networks Corporation) CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information PDF資料下載

參數資料

| 型號: | MT8931CE |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information |

| 中文描述: | 意法半導體的CMOS總線⑩家庭用戶網絡接口電路的初步信息 |

| 文件頁數: | 4/39頁 |

| 文件大小: | 833K |

| 代理商: | MT8931CE |

第1頁第2頁第3頁當前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

MT8931C

Data Sheet

4

Functional Description

The MT8931C Subscriber Network Interface Circuit

(SNIC) is a multifunction transceiver providing a

complete interface to the S/T Reference Point as

specified in ETS 300-012, CCITT Recommendation

I.430 and ANSI T1.605. Implementing both

point-to-point and point-to-multipoint voice/data

transmission, the SNIC may be used at either end of

the digital subscriber loop. A programmable digital

interface allows the MT8931C to be configured as a

Network Termination (NT) or as a Terminal

Equipment (TE) device.

The SNIC supports 192 kbit/s (2B+D + overhead) full

duplex data transmission on a 4-wire balanced

transmission line. Transmission capability for both B

and D channels, as well as related timing and

synchronization functions, are provided on chip. The

signalling capability and procedures necessary to

enable customer terminals (TEs) to be activated and

deactivated,

form

part

functionality. The SNIC handles D-channel resource

allocation and prioritization for access contention

resolution and signalling requirements in passive bus

line configurations. Control and status information

allows implementation of mainten-ance functions

and monitoring of the device and the subscriber loop.

of

the

MT8931C’s

An HDLC transceiver is included on the SNIC for link

access protocol handling via the D-channel.

Depacketized data is passed to and from the

transceiver via the microprocessor port. Two 19 byte

deep FIFOs, one for transmit and one for receive,

are provided to buffer the data. The HDLC block can

be set up to transmit or receive to/from either the

S-interface port or the ST-BUS port. Further, the

transmit destination and receive source can be

independently selected, e.g., transmit to S-interface

while receiving from ST-BUS. The transmit and

receive paths can be separately enabled or disabled.

Both, one and two byte address recognition is

supported by the SNIC. A transparent mode allows

data to be passed directly to the D channel without

being packetized.

A block diagram of the MT8931C is shown in Figure

1. The SNIC has three interface ports: a 4-wire

CCITT compatible S/T interface (subscriber loop

interface), a 2048 kbit/s ST-BUS serial port, and a

general purpose parallel microprocessor port. This

8-bit parallel port is compatible with both Motorola or

Intel microprocessor bus signals and timing.

The three major blocks of the MT8931C, consisting

of the system serial interface (ST-BUS), HDLC

transceiver, and the digital subscriber loop interface

(S-interface) are interconnected by high speed data

busses. Data sent to and received from the

S-interface port (B1, B2 and D channels) can be

accessed from either the parallel microprocessor

port or the serial ST-BUS port. This is also true for

SNIC control and status information (C-channel).

Depacketized D-channel information to and from the

HDLC section can only be accessed through the

parallel microprocessor port.

S-Bus Interface

The S-Bus is a four wire, full duplex, time division

multiplexed transmission facility which exchanges

information at 192 kbit/s rate including two 64 kbit/s

PCM voice or data channels, a 16 kbit/s signalling

channel and 48 kbit/s for synchronization and

overhead. The relative position of these channels

with respect to the ST-BUS is shown in Figures 4

and 5.

The SNIC makes use of the first four channels on the

ST-BUS to transmit and receive control/status and

data to and from the S-interface port. These are the

B, D and C-channels (see Figure 4).

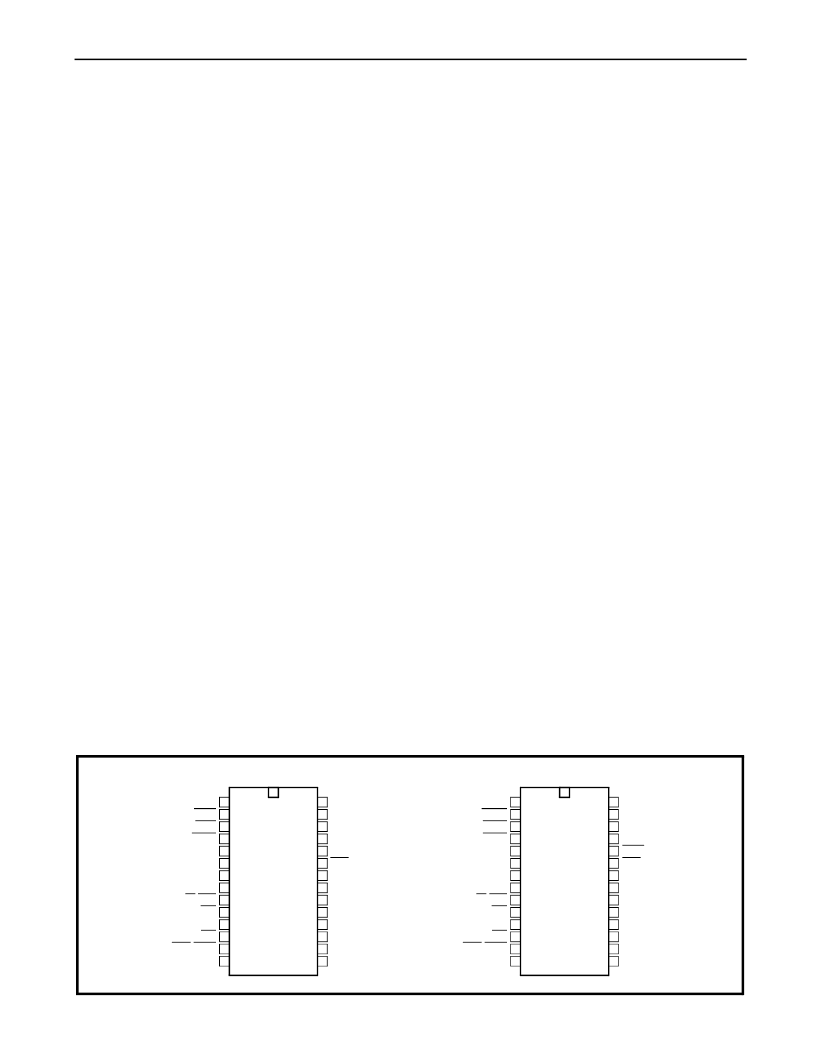

Figure 3 - SNIC Pin Connections

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

28

27

26

25

24

23

22

21

HALF

C4bi

F0bi

F0od

DSTi

DSTo

Cmode

NT

R/W/WR

DS/RD

AS/ALE

CS

IRQ/NDA

VSS

VDD

VBias

LTx

LRx

STAR

Rsti

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

28

27

26

25

24

23

22

21

HALF

C4bo

F0bo

F0od

DSTi

DSTo

XTAL2

XTAL1

R/W/WR

DS/RD

AS/ALE

CS

IRQ/NDA

VSS

VDD

VBias

LTx

LRx

Rsto

Rsti

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

NT MODE

TE MODE

相關PDF資料 |

PDF描述 |

|---|---|

| MT8931C | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information |

| MT8931CC | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information |

| MT8931CP | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit |

| MT8941 | Advanced T1/CEPT Digital Trunk PLL |

| MT8941BE | Advanced T1/CEPT Digital Trunk PLL |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MT8931CP | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Subscriber Network Interface Circuit |

| MT8940 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO-CMOS ST-BUS⑩ FAMILY T1/CEPT Digital Trunk PLL |

| MT8940-1 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO-CMOS ST-BUS⑩ FAMILY T1/CEPT Digital Trunk PLL |

| MT8940AC | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:T1/CEPT Digital Trunk PLL |

| MT8940AE | 制造商:MITEL 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。