- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄25623 > MT80C51C-20R (TEMIC SEMICONDUCTORS) 8-BIT, MROM, 20 MHz, MICROCONTROLLER, PQFP44 PDF資料下載

參數(shù)資料

| 型號(hào): | MT80C51C-20R |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, PQFP44 |

| 文件頁(yè)數(shù): | 86/109頁(yè) |

| 文件大?。?/td> | 10824K |

| 代理商: | MT80C51C-20R |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)當(dāng)前第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)

63

ATtiny20 [DATASHEET]

8235E–AVR–03/2013

Be aware that the COM0x[1:0] bits are not double buffered together with the compare value. Changing the COM0x[1:0]

bits will take effect immediately.

11.6

Compare Match Output Unit

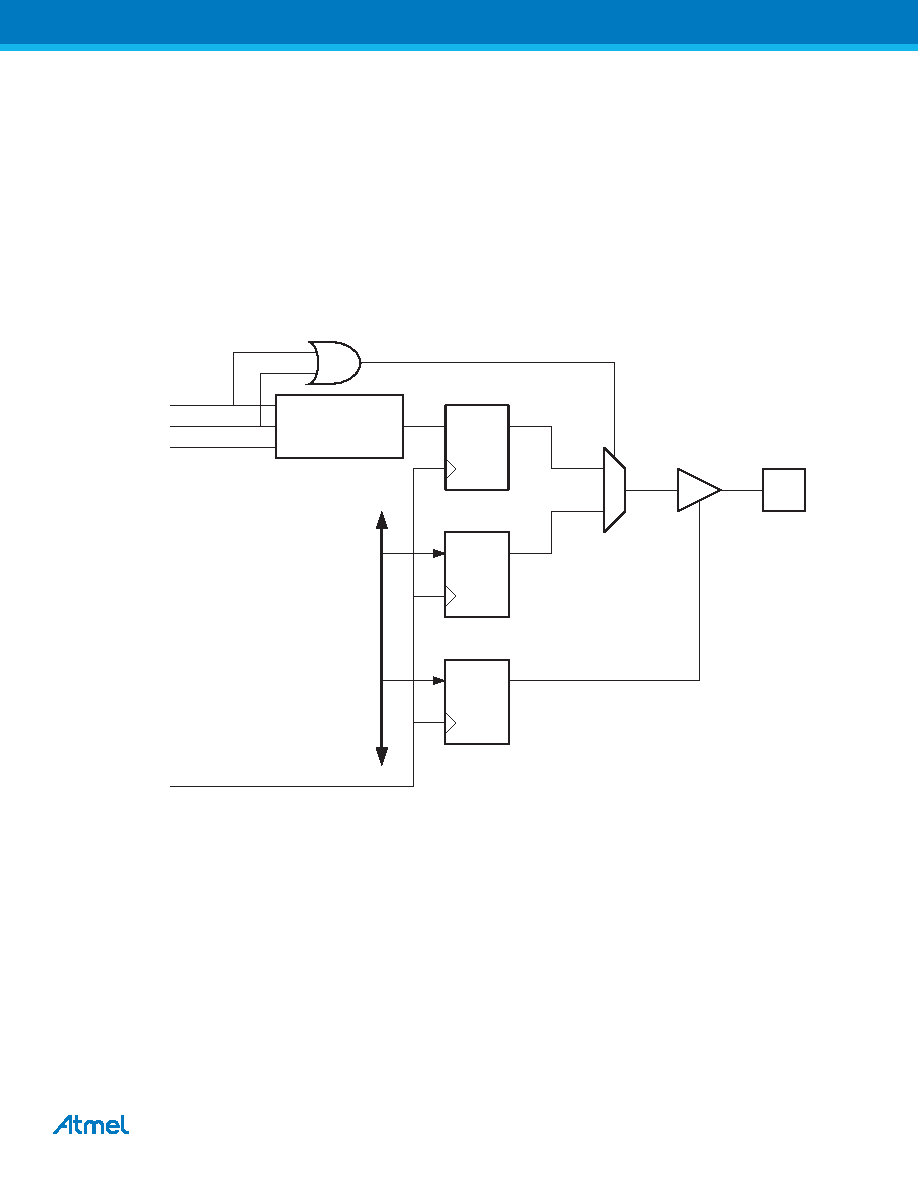

The Compare Output mode (COM0x[1:0]) bits have two functions. The Waveform Generator uses the COM0x[1:0] bits

for defining the Output Compare (OC0x) state at the next Compare Match. Also, the COM0x[1:0] bits control the OC0x

pin output source. Figure 11-4 on page 63 shows a simplified schematic of the logic affected by the COM0x[1:0] bit

setting. The I/O Registers, I/O bits, and I/O pins in the figure are shown in bold. Only the parts of the general I/O Port

Control Registers (DDR and PORT) that are affected by the COM0x[1:0] bits are shown. When referring to the OC0x

state, the reference is for the internal OC0x Register, not the OC0x pin. If a system reset occur, the OC0x Register is

reset to “0”.

Figure 11-4. Compare Match Output Unit, Schematic

The general I/O port function is overridden by the Output Compare (OC0x) from the Waveform Generator if either of the

COM0x[1:0] bits are set. However, the OC0x pin direction (input or output) is still controlled by the Data Direction

Register (DDR) for the port pin. The Data Direction Register bit for the OC0x pin (DDR_OC0x) must be set as output

before the OC0x value is visible on the pin. The port override function is independent of the Waveform Generation mode.

The design of the Output Compare pin logic allows initialization of the OC0x state before the output is enabled. Note that

some COM0x[1:0] bit settings are reserved for certain modes of operation, see “Register Description” on page 69

11.6.1 Compare Output Mode and Waveform Generation

The Waveform Generator uses the COM0x[1:0] bits differently in Normal, CTC, and PWM modes. For all modes, setting

the COM0x[1:0] = 0 tells the Waveform Generator that no action on the OC0x Register is to be performed on the next

Compare Match. For compare output actions in the non-PWM modes refer to Table 11-2 on page 70. For fast PWM

mode, refer to Table 11-3 on page 70, and for phase correct PWM refer to Table 11-4 on page 70.

PORT

DDR

DQ

OCn

Pin

OCnx

DQ

Waveform

Generator

COMnx1

COMnx0

0

1

D

ATA

B

U

S

FOCn

clk

I/O

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MF280C51-36R | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, PQFP44 |

| MQ80C52EXXX-16/883D | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CQFP44 |

| MR80C32-16/883 | 8-BIT, 16 MHz, MICROCONTROLLER, CQCC44 |

| MC80C52TXXX-25SC | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CDIP40 |

| MC80C32-30SHXXX:D | 8-BIT, 30 MHz, MICROCONTROLLER, CDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT80C51FB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MT80C51FB/B | 制造商:Intel 功能描述: |

| MT80GB | 制造商:Datak Corporation 功能描述: |

| MT80JSF1G72NDY-1G1F1A2 | 制造商:Micron Technology Inc 功能描述:8GB 1GX72 DDR3 SDRAM MODULE PBF DIMM 1.5V REGISTERED - Trays |

| MT80KSF1G72NDY-1G4F1A3 | 制造商:Micron Technology Inc 功能描述:8GB 1GX72 DDR3 SDRAM MODULE PBF DIMM 1.35V FULLY BUFFERED - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。