- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄25635 > MR80C52CXXX-12/883:D (TEMIC SEMICONDUCTORS) 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 PDF資料下載

參數(shù)資料

| 型號(hào): | MR80C52CXXX-12/883:D |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 |

| 文件頁(yè)數(shù): | 53/125頁(yè) |

| 文件大小: | 6456K |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)當(dāng)前第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)

218

8021G–AVR–03/11

ATmega329P/3290P

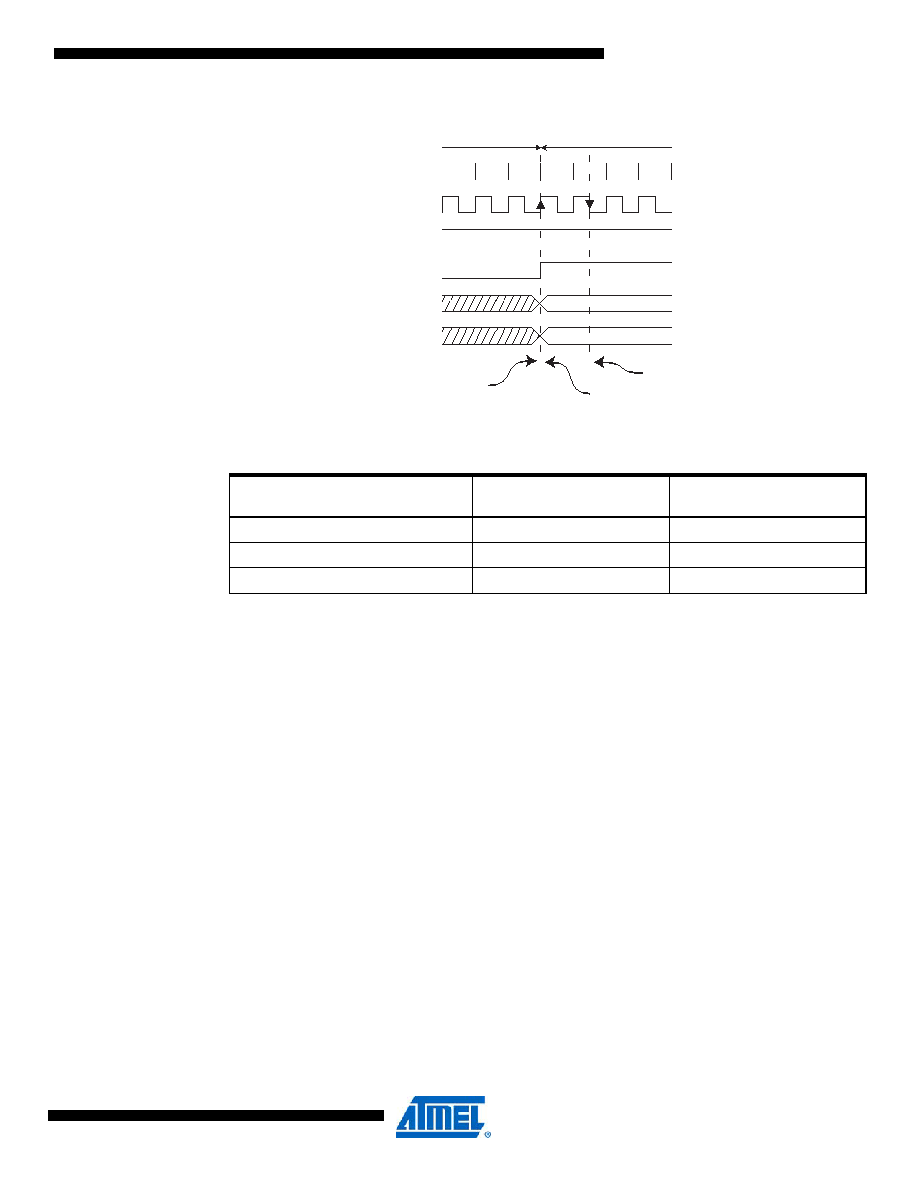

Figure 22-7. ADC Timing Diagram, Free Running Conversion

22.6

Changing Channel or Reference Selection

The MUXn and REFS1:0 bits in the ADMUX Register are single buffered through a temporary

register to which the CPU has random access. This ensures that the channels and reference

selection only takes place at a safe point during the conversion. The channel and reference

selection is continuously updated until a conversion is started. Once the conversion starts, the

channel and reference selection is locked to ensure a sufficient sampling time for the ADC. Con-

tinuous updating resumes in the last ADC clock cycle before the conversion completes (ADIF in

ADCSRA is set). Note that the conversion starts on the following rising ADC clock edge after

ADSC is written. The user is thus advised not to write new channel or reference selection values

to ADMUX until one ADC clock cycle after ADSC is written.

If Auto Triggering is used, the exact time of the triggering event can be indeterministic. Special

care must be taken when updating the ADMUX Register, in order to control which conversion

will be affected by the new settings.

If both ADATE and ADEN is written to one, an interrupt event can occur at any time. If the

ADMUX Register is changed in this period, the user cannot tell if the next conversion is based

on the old or the new settings. ADMUX can be safely updated in the following ways:

When ADATE or ADEN is cleared.

2.

During conversion, minimum one ADC clock cycle after the trigger event.

3.

After a conversion, before the Interrupt Flag used as trigger source is cleared.

When updating ADMUX in one of these conditions, the new settings will affect the next ADC

conversion.

Table 22-1.

ADC Conversion Time

Condition

Sample & Hold (Cycles from

Start of Conversion)

Conversion Time (Cycles)

First conversion

13.5

25

Normal conversions, single ended

1.5

13

Auto Triggered conversions

2

13.5

11

12

13

Sign and MSB of Result

LSB of Result

ADC Clock

ADSC

ADIF

ADCH

ADCL

Cycle Number

12

One Conversion

Next Conversion

34

Conversion

Complete

Sample & Hold

MUX and REFS

Update

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC80C52EXXX-12SC | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CDIP40 |

| MD80C52TXXX-16SHXXX:D | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 |

| MR80C52CXXX-12SCR | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 |

| MQ80C52XXX-25 | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CQFP44 |

| MD80C52EXXX-20SB | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MR80C86 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86/B | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述:Microprocessor, 16 Bit, 44 Pin, Ceramic, LCC |

| MR80C86-2 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86-2/883 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MR80C86-2/B | 制造商:Intersil Corporation 功能描述:MPU 80C86 16BIT CMOS 8MHZ 44PLCC - Rail/Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。