- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45374 > MPC92432AER2 (INTEGRATED DEVICE TECHNOLOGY INC) 1360 MHz, OTHER CLOCK GENERATOR, PQFP48 PDF資料下載

參數(shù)資料

| 型號(hào): | MPC92432AER2 |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘產(chǎn)生/分配 |

| 英文描述: | 1360 MHz, OTHER CLOCK GENERATOR, PQFP48 |

| 封裝: | LEAD FREE, LQFP-48 |

| 文件頁數(shù): | 20/20頁 |

| 文件大小: | 412K |

| 代理商: | MPC92432AER2 |

Advanced Clock Drivers Devices

Freescale Semiconductor

9

MPC92432

Programming the MPC92432

The MPC92432 has a parallel and a serial configuration

interface. The purpose of the parallel interface is to directly

configure the PLL dividers through hardware pins without the

overhead of a serial protocol. At device startup, the device

always obtains an initial PLL frequency configuration through

the parallel interface. The parallel interface does not support

reading the PLL configuration.

The serial interface is I2C compatible. It allows reading and

writing devices settings by accessing internal device

registers. The serial interface is designed for host-controller

access to the synthesizer frequency settings for instance in

frequency-margining applications.

Using the Parallel Interface

The parallel interface supports write-access to the PLL

frequency setting directly through 15 configuration pins (P,

M[9:0], NA[2:0], and NB). The parallel interface must be

enabled by setting PLOAD to logic low level. During

PLOAD = 0, any change of the logical state of the P, M[9:0],

NA[2:0], and NB pins will immediately affect the internal PLL

divider settings, resulting in a change of the internal VCO-

frequency and the output frequency. The parallel interface

mode disables the I2C write-access to the internal registers;

however, I2C read-access to the internal configuration

registers is enabled.

Upon startup, when the device reset signal is released

(rising edge of the MR signal), the device reads its startup

configuration through the parallel interface and independent

on the state of PLOAD. It is recommended to provide a valid

PLL configuration for startup. If the parallel interface pins are

left open, a default PLL configuration will be loaded. After the

low-to-high transition of PLOAD, the configuration pins have

no more effect and the configuration registers are made

accessible through the serial interface.

Using the I2C Interface

PLOAD = 1 enables the programming and monitoring of

the internal registers through the I2C interface. Device

register access (write and read) is possible through the 2-wire

interface using SDA (configuration data) and SCL

(configuration clock) signals. The MPC92432 acts as a slave

device at the I2C bus. For further information on I2C it is

recommended to refer to the I2C bus specification

(version 2.1).

PLOAD = 0 disables the I2C-write-access to the configura-

tion registers and any data written into the register is ignored.

However, the MPC92432 is still visible at the I2C interface

and I2C transfers are acknowledged by the device. Read-ac-

cess to the internal registers during PLOAD = 0 (parallel pro-

gramming mode) is supported.

Note that the device automatically obtains a configuration

using the parallel interface upon the release of the device

reset (rising edge of MR) and independent on the state of

PLOAD. Changing the state of the PLOAD input is not

supported when the device performs any transactions on the

I2C interface.

Programming Model and Register Set

The synthesizer contains two fully accessible configuration

registers (PLL_L and PLL_H) and a write-only command

register (CMD). Programming the synthesizer frequency

through the I2C interface requires two steps: 1) writing a valid

PLL configuration to the configuration registers and 2)

loading the registers into the PLL by an I2C command. The

PLL frequency is affected as a result of the second step.

This two-step procedure can be performed by a single I2C

transaction or by multiple, independent I2C transactions. An

alternative way to achieve small PLL frequency changes is to

use the increment or decrement commands of the

synthesizer, which have an immediate effect on the PLL

frequency.

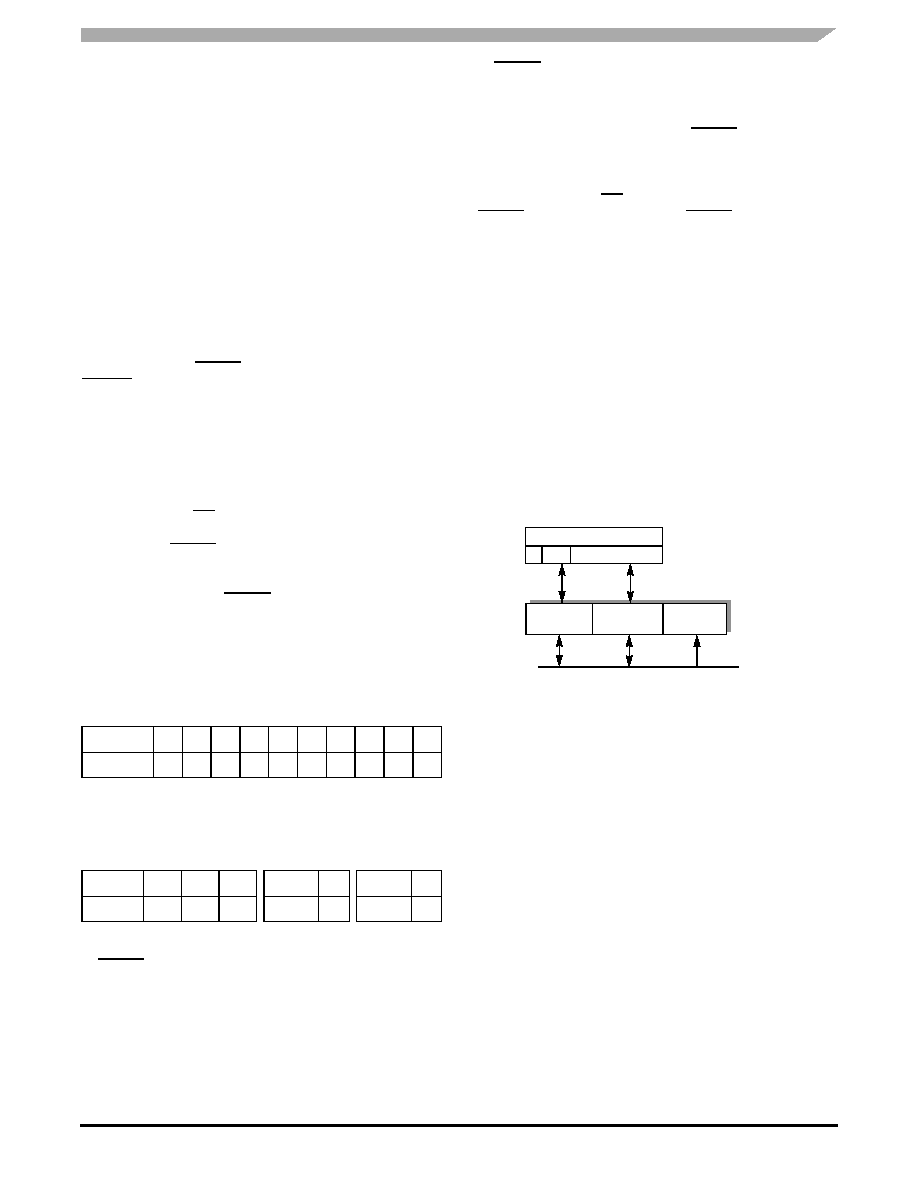

Figure 3. I2C Mode Register Set

Figure 3 illustrates the synthesizer register set. PLL_L and

PLL_H store a PLL configuration and are fully accessible

(Read/Write) by the I2C bus. CMD (Write only) accepts

commands (LOAD, GET, INC, DEC) to update registers and

for direct PLL frequency changes.

Set the synthesizer frequency:

1) Write the PLL_L and PLL_H registers with a new

maps)

2) Write the LOAD command to update the PLL dividers

by the current PLL_L, PLL_H content.

Read the synthesizer frequency:

1) Write the GET commands to update the PLL_L,

PLL_H registers by the PLL divider setting

2) Read the PLL_L, PLL_H registers through I2C

Change the synthesizer frequency in small steps:

1) Write the INC or DEC command to change the PLL

frequency immediately. Repeat at any time if desired.

Table 11. PLL Feedback-Divider Configuration (M)

Feedback

Divider M

9

8765

4321

0

Pin

M9 M8 M7 M6 M5 M4 M3 M2 M1 M0

Default

0

1111

1010

0

Table 12. PLL Pre/Post-Divider Configuration (N, P)

Post-D.

NA

210

Post-D.

NB

NB

Pre-D.

P

P

Pin

NA2

NA1

NA0

Pin

NB

Pin

P

Default

011

Default

0

Default

1

Configuration Latches

I2C Registers

I2C Access

Synthesizer – PLL

PN

M

LOAD/GET

PLL_L (R/W)

0x00

PLL_H (R/W)

0x01

CMD (W)

0xF0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC92432FAR2 | 1360 MHz, OTHER CLOCK GENERATOR, PQFP48 |

| MPC92439EI | 900 MHz, OTHER CLOCK GENERATOR, PQCC28 |

| MPC92439EI | 900 MHz, OTHER CLOCK GENERATOR, PQCC28 |

| MPC92439EIR2 | 900 MHz, OTHER CLOCK GENERATOR, PQCC28 |

| MPC92439FNR2 | 900 MHz, OTHER CLOCK GENERATOR, PQCC28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC92432FA | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:1360 MHz Dual Output LVPECL Clock Synthesizer |

| MPC92433 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:1428 MHz Dual Output LVPECL Clock Synthesizer |

| MPC92433AE | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 FSL 1428MHz Dual Out put LVPECL Clock Syn RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| MPC92433AER2 | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 FSL 1428MHz Dual Out put LVPECL Clock Syn RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| MPC92439 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:900MHz, Low Voltage, LVPECL Clock Syntheesizer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。