- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25631 > MPC8547EPXATJA (FREESCALE SEMICONDUCTOR INC) 32-BIT, 1200 MHz, MICROPROCESSOR, PBGA783 PDF資料下載

參數(shù)資料

| 型號: | MPC8547EPXATJA |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 1200 MHz, MICROPROCESSOR, PBGA783 |

| 封裝: | 29 X 29 MM, 1 MM PITCH, FLIP CHIP, PLASTIC, BGA-783 |

| 文件頁數(shù): | 59/142頁 |

| 文件大小: | 1504K |

| 代理商: | MPC8547EPXATJA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁當前第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 5

Freescale Semiconductor

23

DDR and DDR2 SDRAM

NOTE

For the ADDR/CMD setup and hold specifications in Table 19, it is

assumed that the clock control register is set to adjust the memory clocks by

1/2 applied cycle.

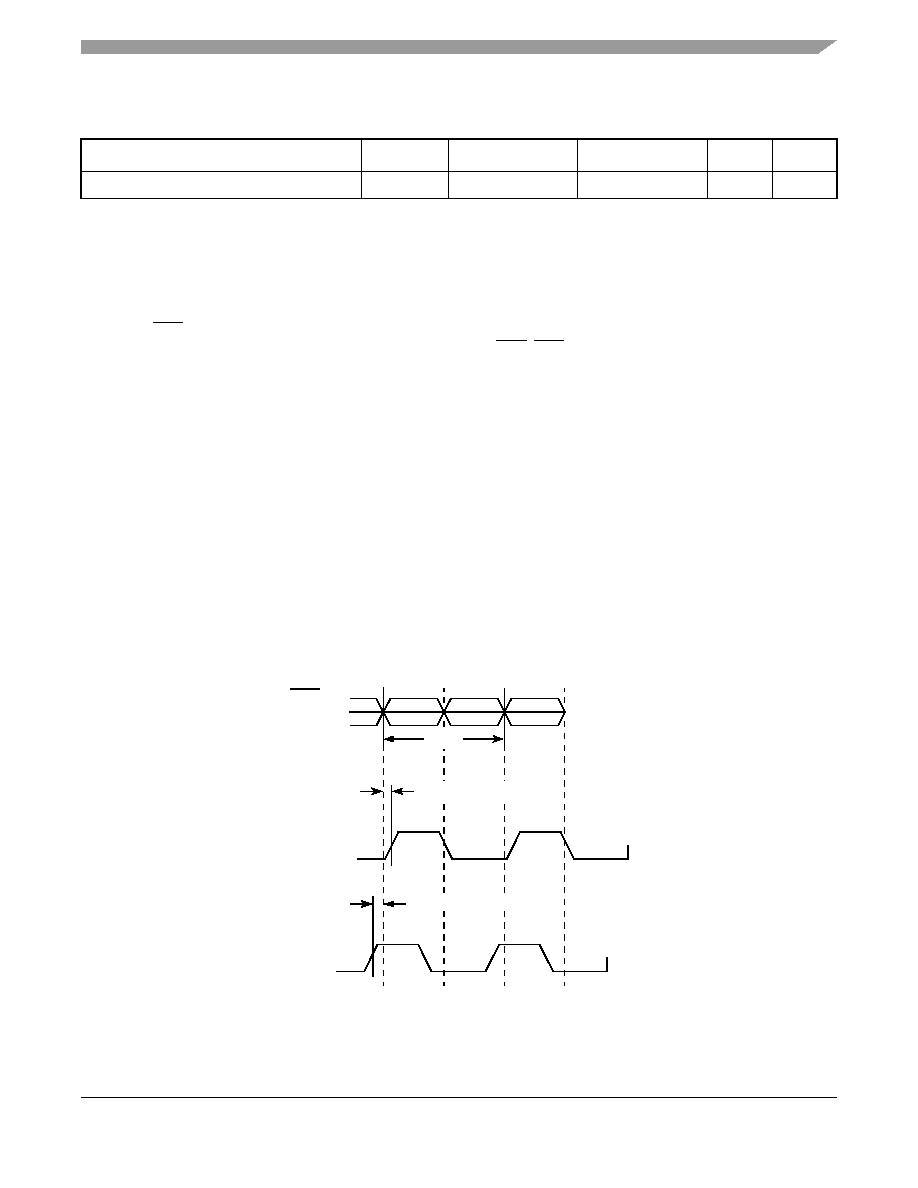

Figure 3. Timing Diagram for tDDKHMH

MDQS epilogue end

tDDKHME

–0.6

0.6

ns

6

Notes:

1. The symbols used for timing specifications follow the pattern of t(first two letters of functional block)(signal)(state)(reference)(state) for

inputs and t(first two letters of functional block)(reference)(state)(signal)(state) for outputs. Output hold time can be read as DDR timing

(DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example,

tDDKHAS symbolizes DDR timing (DD) for the time tMCK memory clock reference (K) goes from the high (H) state until outputs

(A) are setup (S) or output valid time. Also, tDDKLDX symbolizes DDR timing (DD) for the time tMCK memory clock reference

(K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS.

4. Note that tDDKHMH follows the symbol conventions described in note 1. For example, tDDKHMH describes the DDR timing (DD)

from the rising edge of the MCK[

n] clock (KH) until the MDQS signal is valid (MH). tDDKHMH can be modified through control

of the MDQS override bits (called WR_DATA_DELAY) in the TIMING_CFG_2 register. This will typically be set to the same

delay as in DDR_SDRAM_CLK_CNTL[CLK_ADJUST]. The timing parameters listed in the table assume that these 2

parameters have been set to the same adjustment value. See the

MPC8548E PowerQUICC III Integrated Processor

Reference Manual for a description and understanding of the timing modifications enabled by use of these bits.

5. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC

(MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the microprocessor.

6. All outputs are referenced to the rising edge of MCK[

n] at the pins of the microprocessor. Note that tDDKHMP follows the

symbol conventions described in note 1.

Table 19. DDR SDRAM Output AC Timing Specifications (continued)

At recommended operating conditions.

Parameter

Symbol1

Min

Max

Unit

Notes

tDDKHMHmax) = 0.6 ns

MDQS

MCK[

n]

MCK[

n]

tMCK

tDDKHMH(min) = –0.6 ns

MDQS

相關PDF資料 |

PDF描述 |

|---|---|

| MPC8547VUATGA | 32-BIT, 1200 MHz, MICROPROCESSOR, CBGA783 |

| MPC8548CHXATJ | 32-BIT, 1200 MHz, MICROPROCESSOR, CBGA783 |

| MPC8548ECHXAUGA | 32-BIT, 1333 MHz, MICROPROCESSOR, CBGA783 |

| MPC8548EHXAUHA | 32-BIT, 1333 MHz, MICROPROCESSOR, CBGA783 |

| MPC8548EVTAUGB | 32-BIT, 1333 MHz, MICROPROCESSOR, PBGA783 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8547EPXAUJA | 功能描述:微處理器 - MPU PQ3 8547E Storage Processor RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8547EPXAUJB | 功能描述:微處理器 - MPU FG PQ38 8548 RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8547EPXAUJC | 功能描述:微處理器 - MPU REV2.1.3 FG PART 1333 RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8547EPXAUJD | 功能描述:微處理器 - MPU PQ38 PB ST WE 1333 R3.0 RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8547EVTAQGA | 功能描述:微處理器 - MPU PQ3 8547E Storage Processor RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

發(fā)布緊急采購,3分鐘左右您將得到回復。