- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄45359 > MPC8306SCVMADDCA (FREESCALE SEMICONDUCTOR INC) 32-BIT, 266 MHz, RISC PROCESSOR, PBGA369 PDF資料下載

參數(shù)資料

| 型號(hào): | MPC8306SCVMADDCA |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA369 |

| 封裝: | 19 X 19 MM, 1.61 MM HEIGHT, 0.80 MM PITCH, LEAD FREE, MAPBGA-369 |

| 文件頁(yè)數(shù): | 5/71頁(yè) |

| 文件大小: | 452K |

| 代理商: | MPC8306SCVMADDCA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 0

Freescale Semiconductor

13

RESET Initialization

5

RESET Initialization

This section describes the AC electrical specifications for the reset initialization timing requirements of

the MPC8306S. Table 9 provides the reset initialization AC timing specifications for the reset

component(s).

Table 10 provides the PLL lock times.

SYS_CLK_IN duty cycle

tKHK/tSYS_CLK_

IN

40

—

60

%

3

SYS_CLK_IN jitter

—

±150

ps

4, 5

Notes:

1. Caution: The system, core and QUICC Engine block must not exceed their respective maximum or minimum operating

frequencies.

2. Rise and fall times for SYS_CLK_IN are measured at 0.33 and 2.97 V.

3. Timing is guaranteed by design and characterization.

4. This represents the total input jitter—short term and long term—and is guaranteed by design.

5. The SYS_CLK_IN driver’s closed loop jitter bandwidth should be < 500 kHz at –20 dB. The bandwidth must be set low to

allow cascade-connected PLL-based devices to track SYS_CLK_IN drivers with the specified jitter.

6. Spread spectrum is allowed upto 1% down-spread @ 33kHz (max rate).

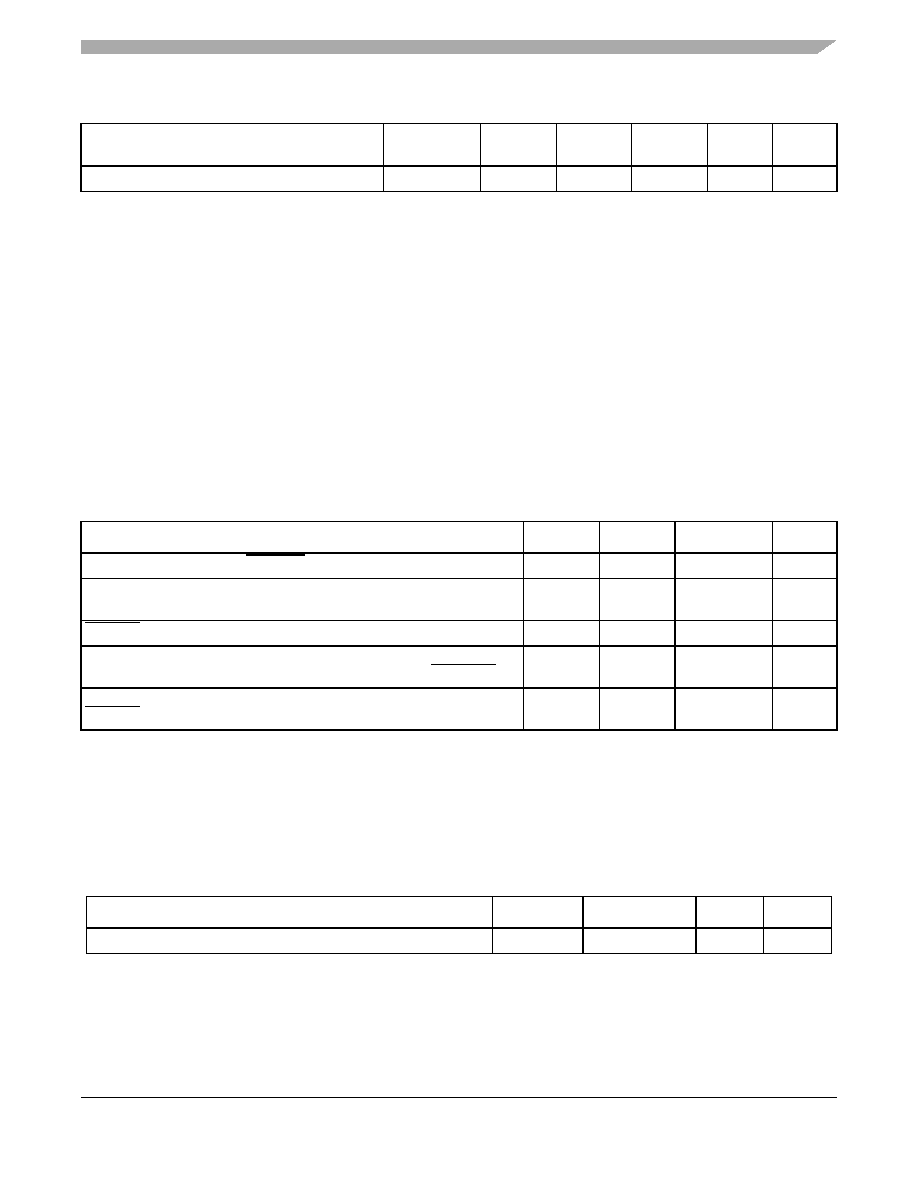

Table 9. RESET Initialization Timing Specifications

Parameter/Condition

Min

Max

Unit

Notes

Required assertion time of HRESET to activate reset flow

32

—

tSYS_CLK_IN

1

Required assertion time of PORESET with stable clock applied to

SYS_CLK_IN

32

—

tSYS_CLK_IN

1

HRESET assertion (output)

512

—

tSYS_CLK_IN

1

Input setup time for POR configuration signals

(CFG_RESET_SOURCE[0:3]) with respect to negation of PORESET

4—

tSYS_CLK_IN

1, 2

Input hold time for POR config signals with respect to negation of

HRESET

0

—

ns

1, 2

Notes:

1. tSYS_CLK_IN is the clock period of the input clock applied to SYS_CLK_IN. For more details, see the MPC8306S

PowerQUICC II Pro Integrated Communications Processor Reference Manual

.

2. POR configuration signals consists of CFG_RESET_SOURCE[0:3].

Table 10. PLL Lock Times

Parameter/Condition

Min

Max

Unit

Notes

PLL lock times

—

100

s—

Table 8. SYS_CLK_IN AC Timing Specifications

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC8306VMACDCA | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA369 |

| MPC8306CVMACDCA | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA369 |

| MPC8306VMABDCA | 32-BIT, 133 MHz, RISC PROCESSOR, PBGA369 |

| MPC8306CVMADDCA | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA369 |

| MPC8308CZQAGD | 32-BIT, 266 MHz, MICROPROCESSOR, PBGA473 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8306SCVMAFDCA | 功能描述:微處理器 - MPU E300 MP ext tmp 333 RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8306SEC | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications |

| MPC8306-SOM | 功能描述:開(kāi)發(fā)板和工具包 - 其他處理器 For MPC8306 Ethernet USB 16bit RoHS:否 制造商:Freescale Semiconductor 產(chǎn)品:Development Systems 工具用于評(píng)估:P3041 核心:e500mc 接口類型:I2C, SPI, USB 工作電源電壓: |

| MPC8306SVMABDC | 制造商:Freescale Semiconductor 功能描述:MPC8306SVMABDC - Bulk |

| MPC8306SVMABDCA | 功能描述:微處理器 - MPU E300 MP 133 RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。