- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45338 > MPC5561MVZ132R (FREESCALE SEMICONDUCTOR INC) MICROCONTROLLER, PBGA324 PDF資料下載

參數(shù)資料

| 型號: | MPC5561MVZ132R |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | MICROCONTROLLER, PBGA324 |

| 封裝: | 23 X 23 MM, 1 MM PITCH, MS-034AAJ-1, LEAD FREE, TEPBGA-324 |

| 文件頁數(shù): | 3/56頁 |

| 文件大小: | 1044K |

| 代理商: | MPC5561MVZ132R |

第1頁第2頁當前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

Electrical Characteristics

MPC5561 Microcontroller Data Sheet, Rev. 2.0

Freescale Semiconductor

11

When powering down, VRC33 and VDDSYN have no delta requirement to each other, because the bypass

capacitors internal and external to the device are already charged. When not powering up or down, no delta

between VRC33 and VDDSYN is required for the VRC to operate within specification.

There are no power up/down sequencing requirements to prevent issues such as latch-up, excessive current

spikes, and so on. Therefore, the state of the I/O pins during power up and power down varies depending

on which supplies are powered.

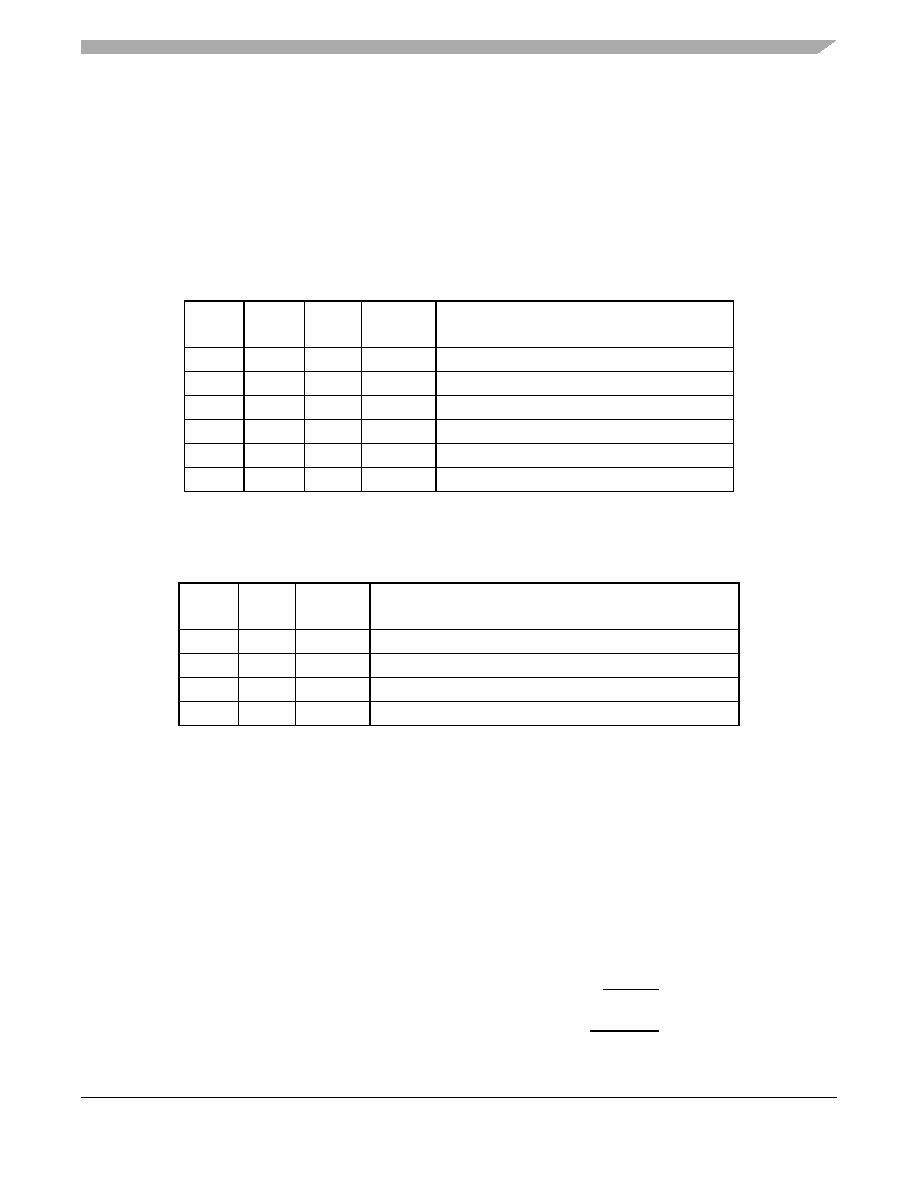

Table 7 gives the pin state for the sequence cases for all pins with pad type pad_fc (fast type).

Table 8 gives the pin state for the sequence cases for all pins with pad type pad_mh (medium type) and

pad_sh (slow type).

The values in Table 7 and Table 8 do not include the effect of the weak-pull devices on the output pins

during power up.

Before exiting the internal POR state, the voltage on the pins goes to high-impedance until POR negates.

When the internal POR negates, the functional state of the signal during reset applies and the weak-pull

devices (up or down) are enabled as defined in the device Reference Manual. If VDD is too low to correctly

propagate the logic signals, the weak-pull devices can pull the signals to VDDE and VDDEH.

To avoid this condition, minimize the ramp time of the VDD supply to a time period less than the time

required to enable the external circuitry connected to the device outputs.

3.7.1

Input Value of Pins During POR Dependent on VDD33

When powering up the device, VDD33 must not lag the latest VDDSYN or RESET power pin (VDDEH6) by

more than the VDD33 lag specification listed in Table 6, spec 8. This avoids accidentally selecting the

bypass clock mode because the internal versions of PLLCFG[0:1] and RSTCFG are not powered and

Table 7. Pin Status for Fast Pads During the Power Sequence

VDDE

VDD33

VDD

POR

Pin Status for Fast Pad Output Driver

pad_fc (fast)

Low

—

Asserted

Low

VDDE

Low

Asserted

High

VDDE

Low

VDD

Asserted

High

VDDE

VDD33

Low

Asserted

High impedance (Hi-Z)

VDDE

VDD33

VDD

Asserted

Hi-Z

VDDE

VDD33

VDD

Negated

Functional

Table 8. Pin Status for Medium and Slow Pads During the Power Sequence

VDDEH

VDD

POR

Pin Status for Medium and Slow Pad Output Driver

pad_mh (medium) pad_sh (slow)

Low

—

Asserted

Low

VDDEH

Low

Asserted

High impedance (Hi-Z)

VDDEH

VDD

Asserted

Hi-Z

VDDEH

VDD

Negated

Functional

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC5566MZP132 | 32-BIT, FLASH, 132 MHz, MICROCONTROLLER, PBGA416 |

| MPC5566MVR80 | 32-BIT, FLASH, 80 MHz, MICROCONTROLLER, PBGA416 |

| MPC5567MZQ112 | FLASH, 112 MHz, MICROCONTROLLER, PBGA324 |

| MPC5567MVZ80 | FLASH, 80 MHz, MICROCONTROLLER, PBGA324 |

| MPC5567MVR112 | FLASH, 112 MHz, MICROCONTROLLER, PBGA416 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC5565 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller |

| MPC5565_08 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller |

| MPC5565AVZ112 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller |

| MPC5565AVZ112R2 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller |

| MPC5565AVZ132 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復。