- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45328 > MK2049-02SI 51.84 MHz, OTHER CLOCK GENERATOR, PDSO20 PDF資料下載

參數(shù)資料

| 型號: | MK2049-02SI |

| 元件分類: | 時鐘產(chǎn)生/分配 |

| 英文描述: | 51.84 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| 封裝: | 0.300 INCH, SOIC-20 |

| 文件頁數(shù): | 4/11頁 |

| 文件大?。?/td> | 136K |

| 代理商: | MK2049-02SI |

MK2049-02/03

Communications Clock PLLs

MDS 2049-02/03 C

2

Revision 091801

Integrated Circuit Systems, Inc. 525 Race Street San Jose CA 95126 (408)295-9800tel www.icst.com

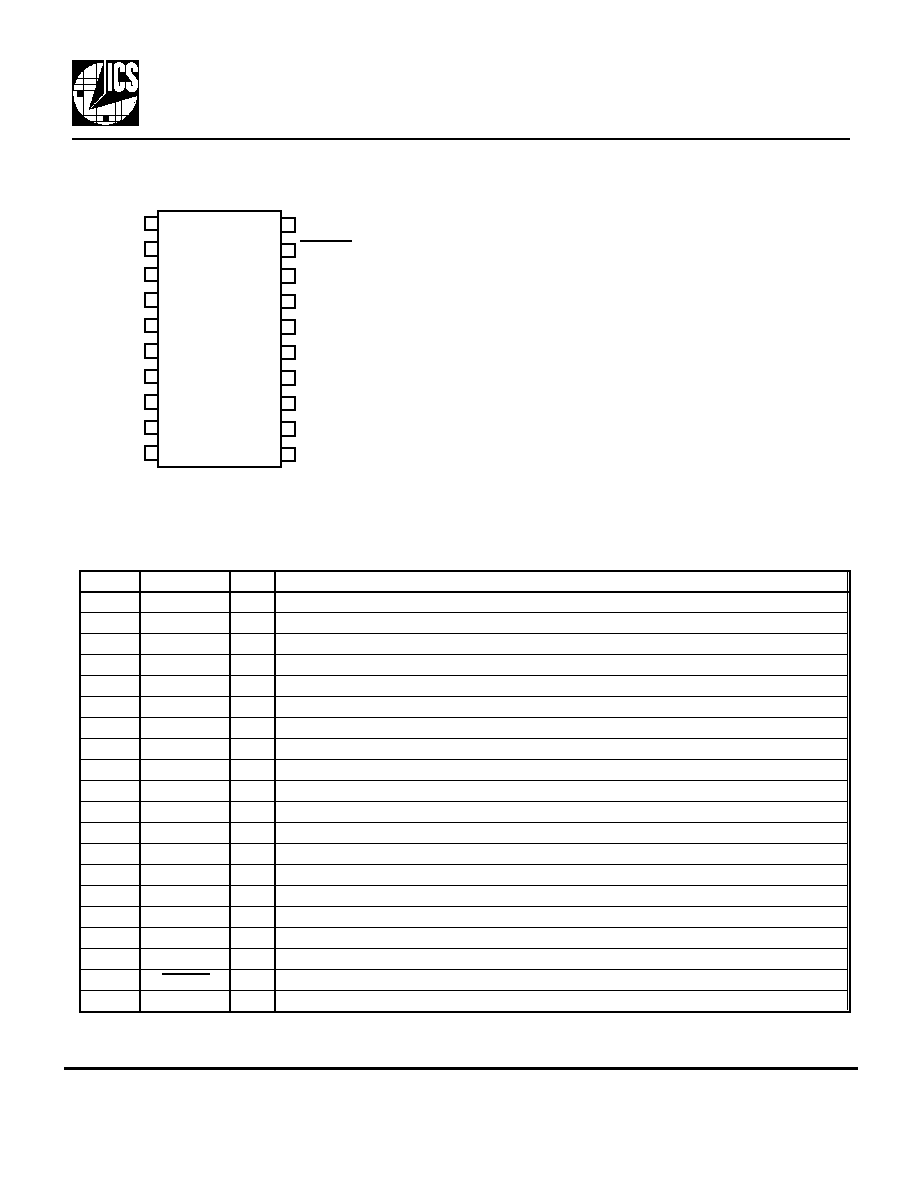

Pin Descriptions

Type:

XI, XO = crystal connections, I = Input, O = output, P = power supply connection, LF = loop filter

connections

Pin Assignment

20 pin (300 mil) SOIC

1

16

2

3

4

15

14

13

VDD

GND

X2

VDD

GND

5

6

7

8

12

11

10

9

FS3

X1

FS1

FS0

CAP1

ICLK

CLK3

CLK1

CLK2

18

17

19

20

VDD

FS2

GND

CAP2

RESET

Number

Name

Type Description

1

FS1

I

Frequency Select 1. Determines CLK input/outputs per tables on pages 4 & 5.

2

X2

XO

Crystal connection. Connect to a MHz crystal as shown in the tables on pages 4 & 5.

3

X1

XI

Crystal connection. Connect to a MHz crystal as shown in the tables on pages 4 & 5.

4

VDD

P

Connect to +5V.

5

VDD

P

Connect to +5V.

6

VDD

P

Connect to +5V.

7

GND

P

Connect to ground.

8

CLK2

O

Clock 2 output determined by status of FS3:0 per tables on pages 4 & 5.

9

CLK1

O

Clock 1 output determined by status of FS3:0 per tables on pages 4 & 5. Always 1/2 of CLK2.

10

CLK3

O

Clock 3 as shown in tables on pages 4 &5; typically recovered 8 kHz clock output.

11

FS2

I

Frequency Select 2. Determines CLK input/outputs per tables on pages 4 & 5.

12

FS3

I

Frequency Select 3. Determines CLK input/outputs per tables on pages 4 & 5.

13

ICLK

I

Input clock connection. Connect to 8 kHz backplane or MHz clock.

14

GND

P

Connect to ground.

15

VDD

P

Connect to +5V.

16

CAP1

LF

Connect the loop filter ceramic capacitors and resistor between this pin and CAP2.

17

GND

P

Connect to ground.

18

CAP2

LF

Connect the loop filter ceramic capacitors and resistor between this pin and CAP1.

19

RESET

I

Reset pin. Resets internal PLL when low. Outputs will stop low. Internal pull-up resistor.

20

FS0

I

Frequency Select 0. Determines CLK input/outputs per tables on pages 4 & 5.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MK2049-11SITR | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-11SITRLF | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-11SITRLF | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-11SI | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-45ASI | 125 MHz, OTHER CLOCK GENERATOR, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MK2049-02SITR | 制造商:ICS 制造商全稱:ICS 功能描述:Communications Clock PLLs |

| MK2049-02STR | 制造商:ICS 制造商全稱:ICS 功能描述:Communications Clock PLLs |

| MK2049-03S | 制造商:MICROCLOCK 功能描述: |

| MK2049-03SI | 制造商:ICS 制造商全稱:ICS 功能描述:Communications Clock PLLs |

| MK2049-03SITR | 制造商:ICS 制造商全稱:ICS 功能描述:Communications Clock PLLs |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。