- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371108 > MH64D72KLG-10 (Mitsubishi Electric Corporation) 4,831,838,208-BIT (67,108,864-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module PDF資料下載

參數(shù)資料

| 型號: | MH64D72KLG-10 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 4,831,838,208-BIT (67,108,864-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| 中文描述: | 4831838208位(67108864 - Word的72位),雙數(shù)據(jù)速率同步DRAM模塊 |

| 文件頁數(shù): | 31/38頁 |

| 文件大?。?/td> | 326K |

| 代理商: | MH64D72KLG-10 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

MITSUBISHI LSIs

MITSUBISHI ELECTRIC

MH64D72KLG-75,-10

4,831,838,208-BIT (67,108,864-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module

MIT-DS-0389-1.1

20.Nov.2000

Preliminary Spec.

Some contents are subject to change without notice.

31

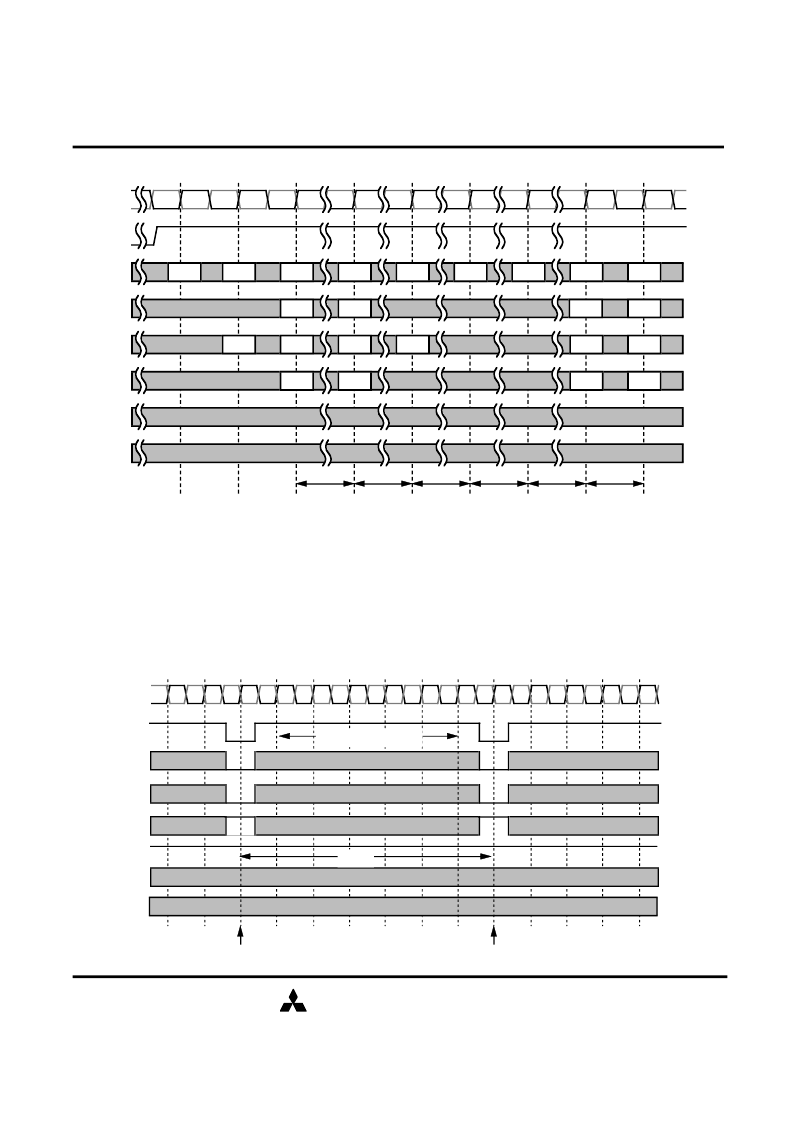

[Initialize and Mode Register sets]

Command

/CLK

CLK

EMRS

PRE

NOP

MRS

PRE

AR

AR

MRS

ACT

Code

Code

Xa

Code

Xa

1 0

Xa

A0-9,11,12

A10

Code

1

BA0,1

DQS

DQ

1

0 0

0 0

Code

tMRD

tMRD

tRP

tRFC

tRFC

tMRD

[AUTO REFRESH]

Single cycle of auto-refresh is initiated with a REFA(/CS=/RAS=/CAS=L,/WE=CKE=H) command. The

refresh address is generated internally. 8192 REFA cycles within 64ms refresh 256Mbits memory cells.

The auto-refresh is performed on 4 banks concurrently. Before performing an auto refresh, all banks must

be in the idle state. Auto-refresh to auto-refresh interval is minimum tRFC . Any command must not be

supplied to the device before tRFC from the REFA command.

Auto-Refresh

/RAS

CKE

/CS

/CAS

/WE

A0-12

BA0,1

NOP or DESELECT

tRFC

Auto Refresh on All Banks

Auto Refresh on All Banks

/CLK

CLK

Code

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MH64D72KLG-75 | 4,831,838,208-BIT (67,108,864-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| MH64D72KLH-10 | 4,831,838,208-BIT (67,108,864-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| MH64D72KLH-75 | 4,831,838,208-BIT (67,108,864-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| MH64S64APFH-6 | 4294967296-BIT (67108864 - WORD BY 64-BIT)SynchronousDRAM |

| MH64S64APFH-6L | 4294967296-BIT (67108864 - WORD BY 64-BIT)SynchronousDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MH64D72KLG-75 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4,831,838,208-BIT (67,108,864-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| MH64D72KLH-10 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4,831,838,208-BIT (67,108,864-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| MH64D72KLH-75 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4,831,838,208-BIT (67,108,864-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| MH64FAD | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:8 pin DIP, 3.3 or 5.0 Volt, HCMOS/TTL Clock Oscillator |

| MH64FAD-R | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:8 pin DIP, 3.3 or 5.0 Volt, HCMOS/TTL Clock Oscillator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。