- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45285 > MC9328MXLCVM15 (FREESCALE SEMICONDUCTOR INC) 32-BIT, 150 MHz, RISC PROCESSOR, PBGA256 PDF資料下載

參數(shù)資料

| 型號: | MC9328MXLCVM15 |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 150 MHz, RISC PROCESSOR, PBGA256 |

| 封裝: | 14 X 14 MM, 1.30 MM HEIGHT, 0.80 MM PITCH, ROHS COMPLIANT, MAPBGA-256 |

| 文件頁數(shù): | 50/90頁 |

| 文件大小: | 1242K |

| 代理商: | MC9328MXLCVM15 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁當(dāng)前第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁

Functional Description and Application Information

MC9328MXL Technical Data, Rev. 8

54

Freescale Semiconductor

4.4.4

Non-TFT Panel Timing

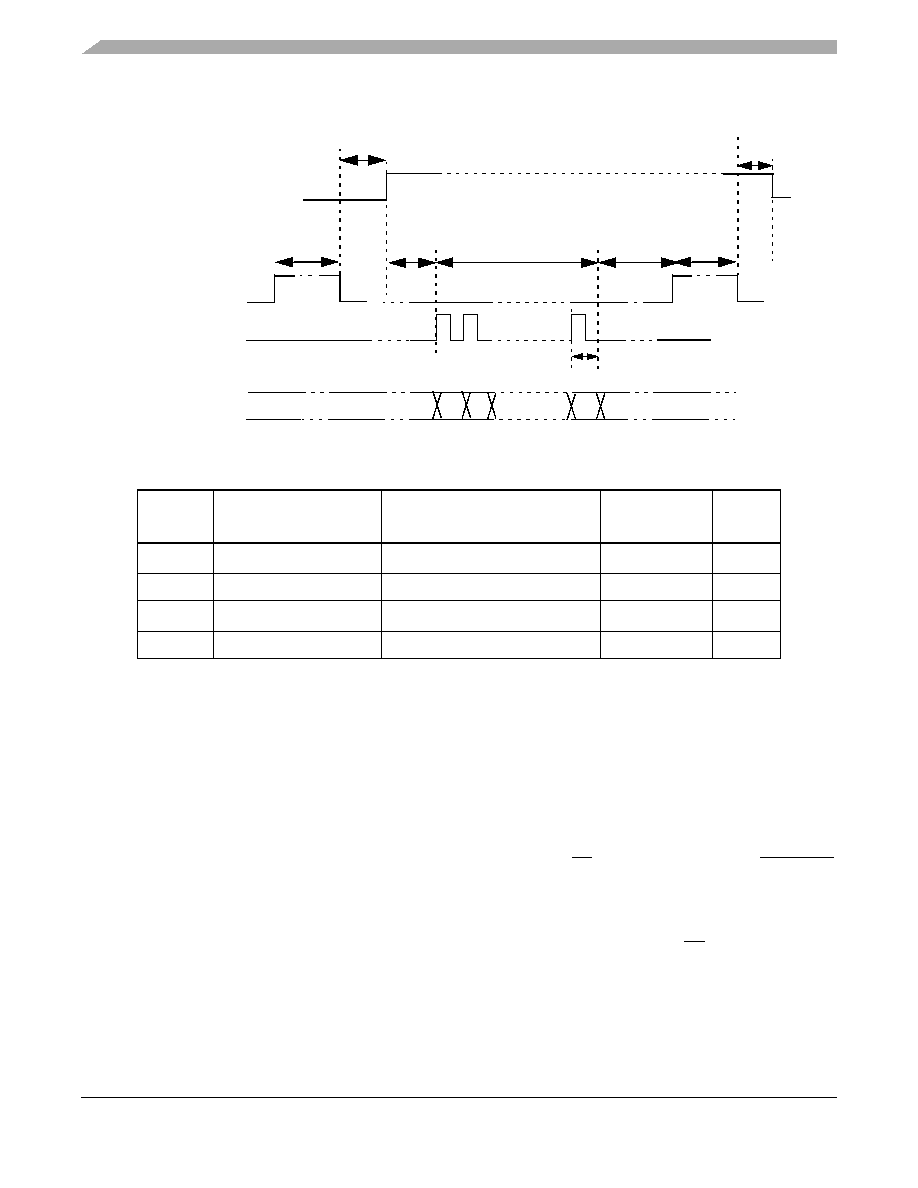

Figure 33. Non-TFT Panel Timing

4.5

SPI Timing Diagrams

To use the internal transmit (TX) and receive (RX) data FIFOs when the SPI 1 module is configured as a

master, two control signals are used for data transfer rate control: the SS signal (output) and the SPI_RDY

signal (input). The SPI1 Sample Period Control Register (PERIODREG1) and the SPI2 Sample Period

Control Register (PERIODREG2) can also be programmed to a fixed data transfer rate for either SPI 1 or

SPI 2. When the SPI 1 module is configured as a slave, the user can configure the SPI1 Control Register

(CONTROLREG1) to match the external SPI master’s timing. In this configuration, SS becomes an input

signal, and is used to latch data into or load data out to the internal data shift registers, as well as to

increment the data FIFO. Figure 34 through Figure 38 show the timing relationship of the master SPI using

different triggering mechanisms.

Table 17. Non TFT Panel Timing Diagram

Symbol

Parameter

Allowed Register

Minimum Value1, 2

1 Maximum frequency of LCDC_CLK is 48 MHz, which is controlled by Peripheral Clock Divider Register.

2 Maximum frequency of SCLK is HCLK / 5, otherwise LD output will be wrong.

Actual Value

Unit

T1

HSYN to VSYN delay3

3 VSYN, HSYN and SCLK can be programmed as active high or active low. In the above timing diagram, all

these 3 signals are active high.

0HWAIT2+2

Tpix4

4 Tpix is the pixel clock period which equals LCDC_CLK period * (PCD + 1).

T2

HSYN pulse width

0

HWIDTH+1

Tpix

T3

VSYN to SCLK

–

0

≤ T3 ≤ Ts5

5 Ts is the shift clock period. Ts = Tpix * (panel data bus width).

–

T4

SCLK to HSYN

0

HWAIT1+1

Tpix

T1

T2

T4

T3

XMAX

VSYN

SCLK

HSYN

LD[15:0]

T2

T1

Ts

Because

of

an

order

from

the

United

States

International

Trade

Commission,

BGA-packaged

product

lines

and

part

numbers

indicated

here

currently

are

not

available

from

Freescale

for

import

or

sale

in

the

United

States

prior

to

September

2010:

i.MXL

Product

Family

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC9328MXLDVP15R2 | 32-BIT, 150 MHz, RISC PROCESSOR, PBGA225 |

| MC9328MXLVP15R2 | 32-BIT, 150 MHz, RISC PROCESSOR, PBGA225 |

| MC9328MXLVM15 | 32-BIT, 150 MHz, RISC PROCESSOR, PBGA256 |

| MC9328MXLDVM20 | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA256 |

| MC9328MXLDVP20R2 | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA225 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC9328MXLCVM15 | 制造商:Freescale Semiconductor 功能描述:Microprocessor |

| MC9328MXLCVM15R2 | 功能描述:處理器 - 專門應(yīng)用 DRAGONBALL CORSICA PB-FR RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| MC9328MXLCVP15 | 功能描述:處理器 - 專門應(yīng)用 DRAGONBALL MXL 225 PB-FR RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| MC9328MXLCVP15 | 制造商:Freescale Semiconductor 功能描述:Microprocessor |

| MC9328MXLCVP15R2 | 功能描述:處理器 - 專門應(yīng)用 DRAGONBALL MXL 225 PB-FR RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。