- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359142 > MC68HC705J1ACP (MOTOROLA INC) Microcontrollers PDF資料下載

參數(shù)資料

| 型號: | MC68HC705J1ACP |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Microcontrollers |

| 中文描述: | 8-BIT, OTPROM, 2.1 MHz, MICROCONTROLLER, PDIP20 |

| 封裝: | PLASTIC, DIP-20 |

| 文件頁數(shù): | 19/108頁 |

| 文件大小: | 718K |

| 代理商: | MC68HC705J1ACP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁

Pin Functions

MC68HC705KJ1 MC68HRC705KJ1 MC68HLC705KJ1 Data Sheet, Rev. 4.1

Freescale Semiconductor

19

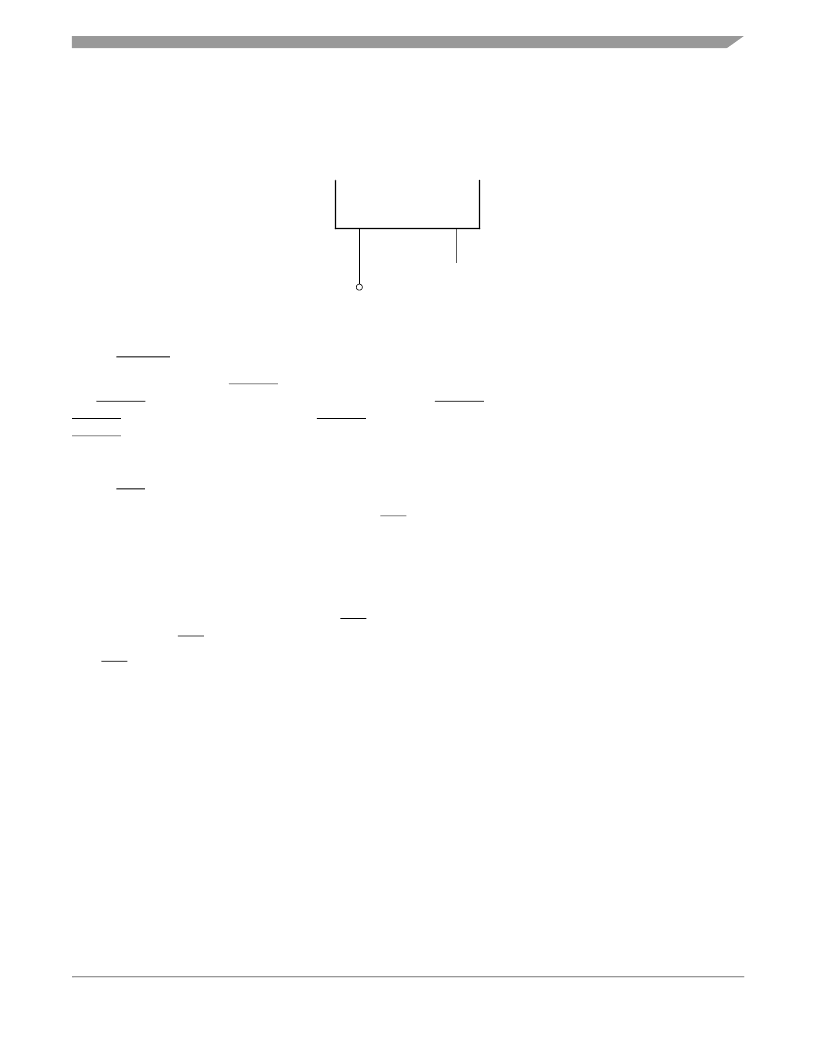

1.4.2.4 External Clock

An external clock from another CMOS-compatible device can be connected to the OSC1 input, with the

OSC2 input not connected, as shown in

Figure 1-8

. This configuration is possible regardless of whether

the crystal/ceramic resonator or the RC oscillator is enabled.

Figure 1-8. External Clock Connections

1.4.3 RESET

Applying a logic 0 to the RESET pin forces the MCU to a known startup state. An internal reset also pulls

the RESET pin low. An internal resistor to V

DD

pulls the RESET pin high. A steering diode between the

RESET and V

DD

pins discharges any RESET pin voltage when power is removed from the MCU. The

RESET pin contains an internal Schmitt trigger to improve its noise immunity as an input. Refer to

Chapter 8 Resets and Interrupts

for more information.

1.4.4 IRQ/V

PP

The external interrupt/programming voltage pin (IRQ/V

PP

) drives the asynchronous IRQ interrupt function

of the CPU. Additionally, it is used to program the user EPROM and mask option register. (See

Chapter 2 Memory

and

Chapter 5 External Interrupt Module (IRQ)

.)

The LEVEL bit in the mask option register provides negative edge-sensitive triggering or both negative

edge-sensitive and low level-sensitive triggering for the interrupt function.

If level-sensitive triggering is selected, the IRQ/V

PP

input requires an external resistor to V

DD

for wired-OR

operation. If the IRQ/V

PP

pin is not used, it must be tied to the V

DD

supply.

The IRQ/V

PP

pin contains an internal Schmitt trigger as part of its input to improve noise immunity. The

voltage on this pin should not exceed V

DD

except when the pin is being used for programming the

EPROM.

NOTE

The mask option register can enable the PA0

–

PA3

pins to function as

external interrupt pins.

1.4.5 PA0–PA7

These eight input/output (I/O) lines comprise port A, a general-purpose bidirectional I/O port. (See

Chapter 5 External Interrupt Module (IRQ)

for information on PA0–PA3 external interrupts.)

1.4.6 PB2 and PB3

These two I/O lines comprise port B, a general-purpose bidirectional I/O port.

MCU

EXTERNAL

CMOS CLOCK

O

O

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC705J1ACDW | Microcontrollers |

| MC68HC705V12CFN | The Motorola microcontroller |

| MC68HC705V12 | The Motorola microcontroller |

| MC68HC705JJ7 | HCMOS Microcontroller Unit |

| MC68HC705SP7 | HCMOS Microcontroller Unit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC705J1ACPE | 功能描述:8位微控制器 -MCU HCO5 CORE+1.2K RAM + EPR RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| MC68HC705J2CDW | 制造商:Motorola Inc 功能描述: 制造商:Motorola Inc 功能描述:MicroController, 8-Bit, 20 Pin, Plastic, SOP |

| MC68HC705J2DW | 制造商:Motorola Inc 功能描述: |

| MC68HC705J5ACP | 制造商:Motorola Inc 功能描述: 制造商:MOTOROLA 功能描述: |

| MC68HC705JB4DW | 制造商:Motorola Inc 功能描述: 制造商:MOTOROLA 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。