- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45232 > MC68HC11P2BCFN4R2 (MOTOROLA INC) 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQCC84 PDF資料下載

參數(shù)資料

| 型號(hào): | MC68HC11P2BCFN4R2 |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQCC84 |

| 封裝: | PLASTIC, LCC-84 |

| 文件頁(yè)數(shù): | 108/236頁(yè) |

| 文件大小: | 1232K |

| 代理商: | MC68HC11P2BCFN4R2 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)當(dāng)前第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)第222頁(yè)第223頁(yè)第224頁(yè)第225頁(yè)第226頁(yè)第227頁(yè)第228頁(yè)第229頁(yè)第230頁(yè)第231頁(yè)第232頁(yè)第233頁(yè)第234頁(yè)第235頁(yè)第236頁(yè)

MOTOROLA

11-14

MC68HC11P2

CPU CORE AND INSTRUCTION SET

11

SUBA (opr)

Subtract memory from A

A M

A

A

IMM

A

DIR

A

EXT

A

IND, X

A

IND, Y

80

90

B0

A0

18 A0

ii

dd

hh ll

ff

2

3

4

5

SUBB (opr)

Subtract memory from B

B M

B

B

IMM

B

DIR

B

EXT

B

IND, X

B

IND, Y

C0

D0

F0

E0

18 E0

ii

dd

hh ll

ff

2

3

4

5

SUBD (opr)

Subtract memory from D

D M:M+1

D

IMM

DIR

EXT

IND, X

IND, Y

83

93

B3

A3

18 A3

jj

kk

dd

hh ll

ff

4

5

6

7

SWI

Software interrupt

see Figure 11-2

INH

3F

14

1

TAB

Transfer A to B

A

B

INH

16

2

0

TAP

Transfer A to CC register

A

CCR

INH

06

2

↓

TBA

Transfer B to A

B

A

INH

17

2

0

TEST

Test (only in test modes)

address bus increments

INH

00

TPA

Transfer CC register to A

CCR

A

INH

07

2

TST (opr)

Test for zero or minus

M 0

EXT

IND, X

IND, Y

7D

6D

18 6D

hh ll

ff

6

7

00

TSTA

Test A for zero or minus

A 0

A

INH

4D

2

00

TSTB

Test B for zero or minus

B 0

B

INH

5D

2

00

TSX

Transfer stack pointer to X

SP + 1

IX

INH

30

3

TSY

Transfer stack pointer to Y

SP + 1

IY

INH

18 30

4

TXS

Transfer X to stack pointer

IX 1

SP

INH

35

3

TYS

Transfer Y to stack pointer

IY 1

SP

INH

18 35

4

WAI

Wait for interrupt

stack registers & WAIT

INH

3E

à

XGDX

Exchange D with X

IX

D; D IX

INH

8F

3

XGDY

Exchange D with Y

IY

D; D IY

INH

18 8F

4

Operators

Operands

Is transferred to

dd

8-bit direct address ($0000$00FF); the high byte is assumed

Boolean AND

to be zero

+

Arithmetic addition, except where used as an

ff

8-bit positive offset ($00 to $FF (0 to 256)) is added to the

inclusive-OR symbol in Boolean formulae

contents of the index register

⊕ Exclusive-OR

hh

High order byte of 16-bit extended address

*

Multiply

ii

One byte of immediate data

:

Concatenation

jj

High order byte of 16-bit immediate data

Arithmetic subtraction, or negation symbol

kk

Low order byte of 16-bit immediate data

(Twos complement)

ll

Low order byte of 16-bit extended address

mm

8-bit mask (set bits to be affected)

rr

Signed relative offset ($80 to $7F (128 to +127));

offset is relative to the address following the offset byte

Cycles

Condition Codes

Innite, or until reset occurs

Bit not changed

à

12 cycles are used, beginning with the opcode

0

Bit always cleared

fetch. A wait state is entered, which remains

1

Bit always set

in effect for an integer number of MPU E clock

Bit set or cleared, depending on the operation

cycles (n) until an interrupt is recognized.

↓ Bit can be cleared, but cannot become set

Finally, two additional cycles are used to fetch

?

Not dened

the appropriate interrupt vector. (14 + n, total).

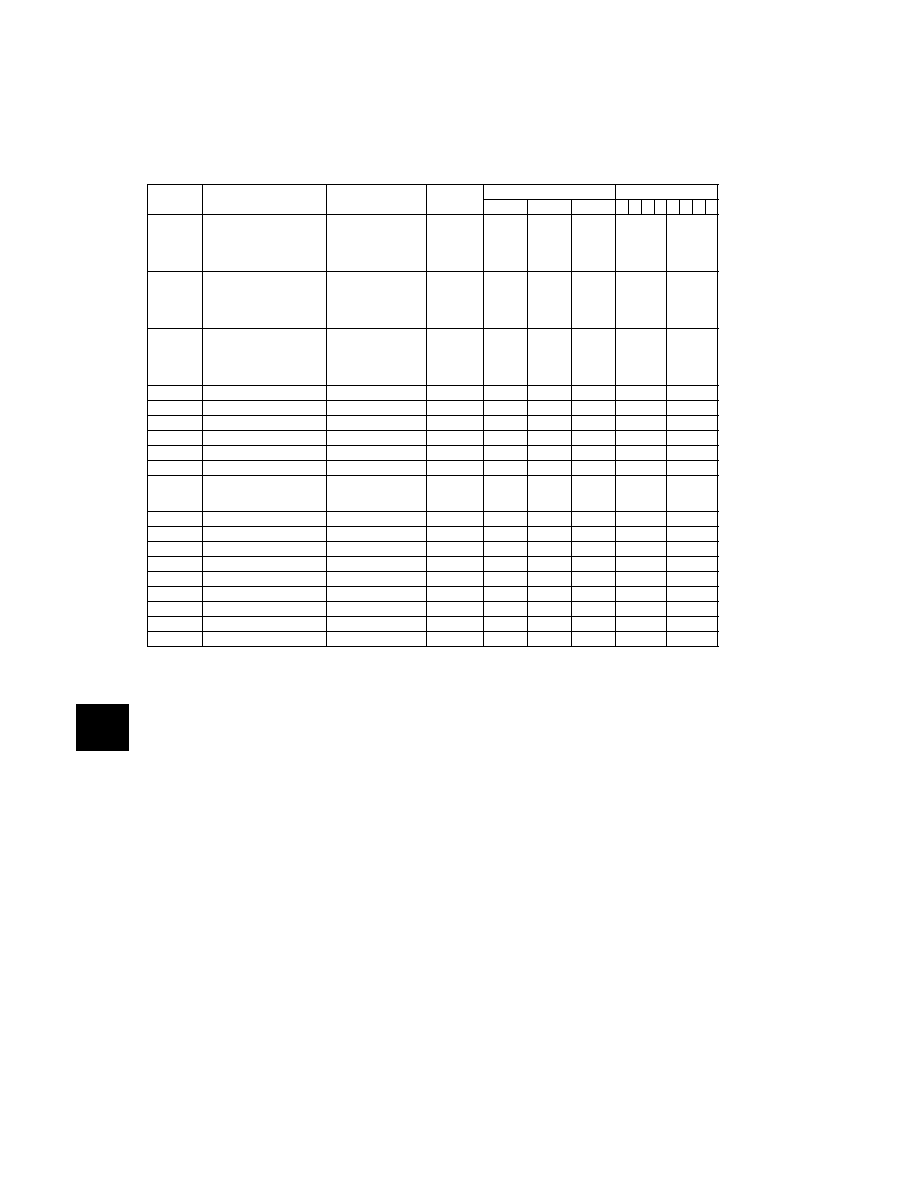

Table 11-2 Instruction set (Sheet 6 of 6)

Mnemonic

Operation

Description

Addressing

mode

Instruction

Condition codes

Opcode

Operand

Cycles

S X H

I

N Z V C

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC11PH8CPV3 | 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PQFP112 |

| MC68S711PH8CFN4 | 8-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PQCC84 |

| MC68S711PH8CFS3 | 8-BIT, UVPROM, 3 MHz, MICROCONTROLLER, CQCC84 |

| MC68S11PH8CPV4 | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP112 |

| MC68S711PH8CFS4 | 8-BIT, UVPROM, 4 MHz, MICROCONTROLLER, CQCC84 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC16Z1CAG | 制造商:Freescale Semiconductor 功能描述: |

| MC68HC16Z1CAG16 | 功能描述:16位微控制器 - MCU 16 BIT MCU 1K RAM RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

| MC68HC16Z1CAG16 | 制造商:Freescale Semiconductor 功能描述:IC16-BIT MICROCONTROLLER |

| MC68HC16Z1CAG20 | 功能描述:16位微控制器 - MCU 16 BIT MCU 1K RAM RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

| MC68HC16Z1CAG20 | 制造商:Freescale Semiconductor 功能描述:Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。