- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371051 > MC68HC11K1MFN2 (MOTOROLA INC) 8-BIT MICROCONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | MC68HC11K1MFN2 |

| 廠(chǎng)商: | MOTOROLA INC |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT MICROCONTROLLER |

| 中文描述: | 8-BIT, MROM, 2 MHz, MICROCONTROLLER, PQCC84 |

| 封裝: | PLASTIC, LCC-84 |

| 文件頁(yè)數(shù): | 12/80頁(yè) |

| 文件大小: | 420K |

| 代理商: | MC68HC11K1MFN2 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)

MOTOROLA

12

M68HC11 K Series

MC68HC11KTS/D

RBOOT — Read Bootstrap ROM/EPROM

Valid only when SMOD is set (bootstrap or special test mode). Can only be written in special modes.

0 = Bootstrap ROM disabled and not in map

1 = Bootstrap ROM enabled and in map at $BE00–$BFFF

SMOD and MDA —Special Mode Select and Mode Select A

These two bits can be read at any time. They can be written anytime in special modes. MDA can only

be written once in normal modes. SMOD cannot be set once it has been cleared.

PSEL[4:0] —Priority Select Bits [4:0]

Refer to

5 Resets and Interrupts

.

*Can be written only once in normal modes. Can be written anytime in special modes.

LIRDV —LIR Driven

In single-chip and bootstrap modes, this bit has no meaning or effect. The LIR pin is normally configured

for wired-OR operation (only pulls low). In order to detect consecutive instructions in a high-speed ap-

plication, this signal can be made to drive high for a short time to prevent false triggering.

0 = LIR not driven high out of reset

1 = LIR driven high for one quarter cycle to reduce transition time

CWOM —Port C Wired-OR Mode

Refer to

6 Parallel Input/Output

.

Bit 5 —Not implemented

Always read zero

IRVNE —Internal Read Visibility/Not E

IRVNE can be written only once in normal modes (SMOD = 0). In special modes IRVNE can be written

any time. In special test mode, IRVNE is reset to one. In all other modes, IRVNE is reset to zero.

In expanded modes this bit determines whether IRV is on or off.

0 = No internal read visibility on external bus

1 = Data from internal reads is driven out the external data bus.

In single-chip modes this bit determines whether the E clock drives out from the chip.

0 = E is driven out from the chip.

1 = E pin is driven low. Refer to the following table.

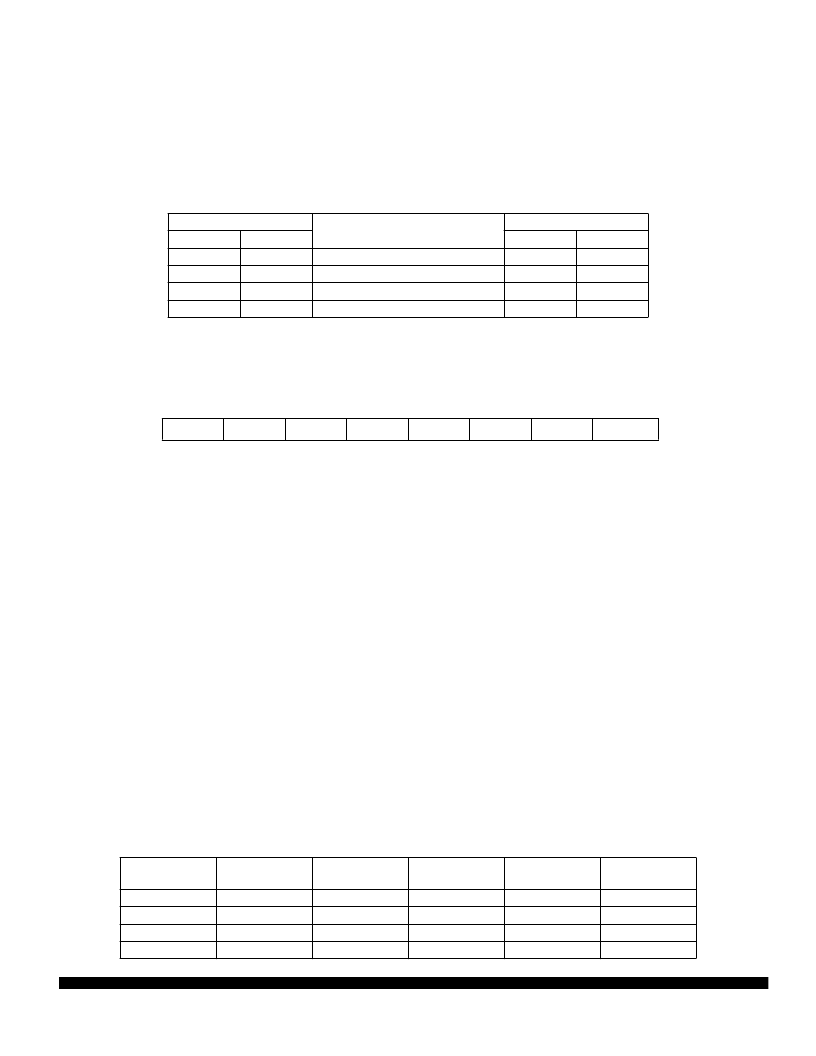

Inputs

Latched at Reset

SMOD

0

0

1

1

MODB

1

1

0

0

MODA

0

1

0

1

Mode

Single Chip

Expanded

Bootstrap

Special Test

MDA

0

1

0

1

OPT2 —

System Configuration Options 2

$0038

Bit 7

6

5

4

3

2

1

Bit 0

LIRDV

CWOM

—

IRVNE*

LSBF

SPR2

XDV1

XDV0

RESET:

0

0

0

—

0

0

0

0

Mode

IRVNE Out

of Reset

0

0

0

1

E Clock Out

of Reset

On

On

On

On

IRV Out of

Reset

Off

Off

Off

On

IRVNE

Affects Only

E

IRV

E

IRV

IRVNE Can

Be Written

Once

Once

Anytime

Anytime

Single Chip

Expanded

Boot

Special Test

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC11K1MFN3 | Aluminum Electrolytic Radial Lead 5mm Length Capacitor; Capacitance: 33uF; Voltage: 50V; Case Size: 8x5 mm; Packaging: Bulk |

| MC68HC11K1MFN4 | 8-BIT MICROCONTROLLER |

| MC68HC11K1CFU3 | 8-BIT MICROCONTROLLER |

| MC68HC11K4CFU3 | Technical Summary 8-Bit Microcontroller |

| MC68HC11K4BCFU4 | 8-BIT MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC11K1MFN3 | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:Technical Summary 8-Bit Microcontroller |

| MC68HC11K1MFN4 | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:8-Bit Microcontroller |

| MC68HC11K1VFN2 | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:8-Bit Microcontroller |

| MC68HC11K1VFN3 | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:Technical Summary 8-Bit Microcontroller |

| MC68HC11K1VFN4 | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。