- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45360 > MPC8313ZQAGD (FREESCALE SEMICONDUCTOR INC) 32-BIT, 400 MHz, MICROPROCESSOR, PBGA516 PDF資料下載

參數(shù)資料

| 型號: | MPC8313ZQAGD |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA516 |

| 封裝: | 27 X 27 MM, 2.25 MM HEIGHT, 1 MM PITCH, TEPBGAII-516 |

| 文件頁數(shù): | 74/100頁 |

| 文件大小: | 1247K |

| 代理商: | MPC8313ZQAGD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁當(dāng)前第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁

MPC8313E PowerQUICC II Pro Processor Hardware Specifications, Rev. 3

Freescale Semiconductor

75

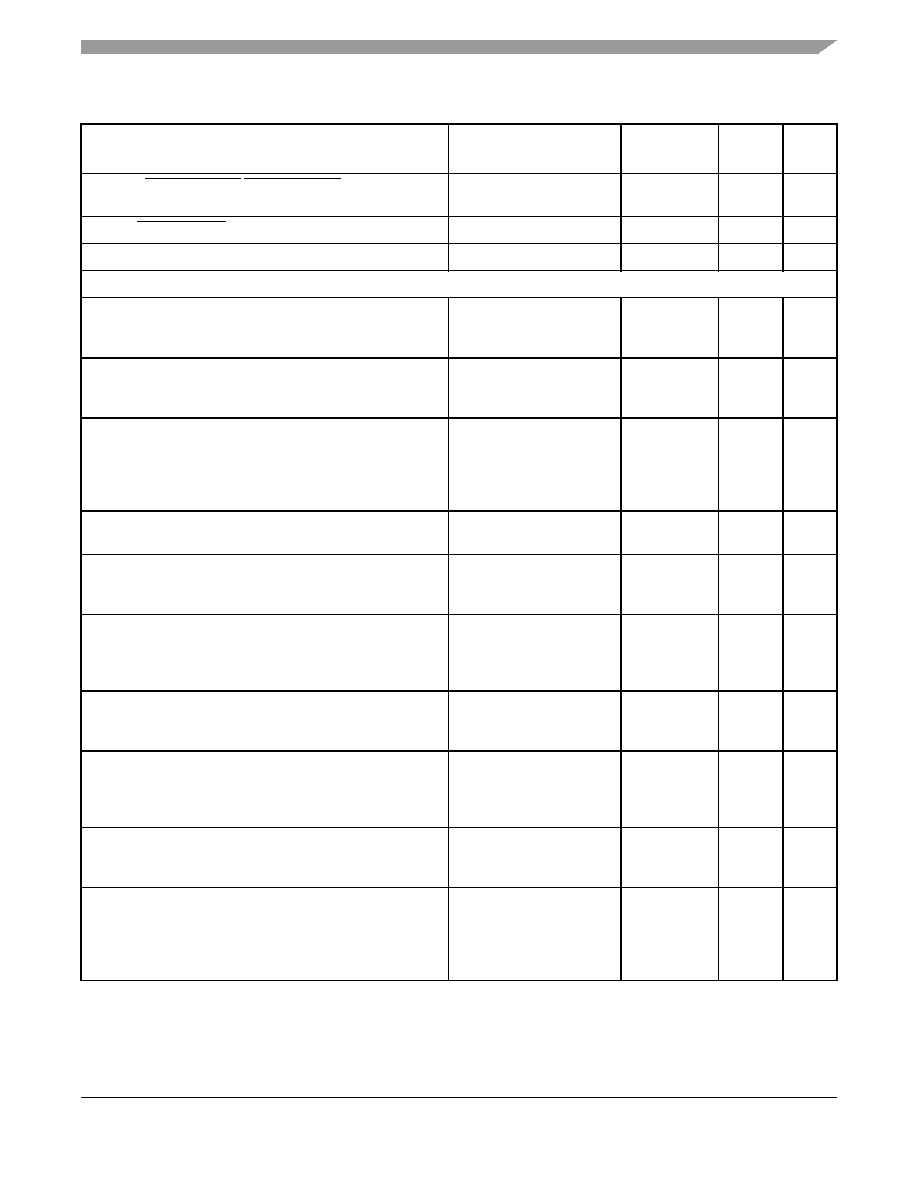

Package and Pin Listings

SPIMISO/GTM1_TGATE3/GTM2_TGATE4/GPIO29/

LDVAL

H3

IO

NVDD

SPICLK/GTM1_TOUT3/GPIO30

G1

IO

NVDD

SPISEL/GPIO31

G3

IO

NVDD

Power and Ground Supplies

AVDD1

F14

Power for e300

core APLL

(1.0 V)

—

AVDD2

P21

Power for

system APLL

(1.0 V)

—

GVDD

A2,A3,A4,A24,A25,B3,

B4,B5,B12,B13,B20,B21,

B24,B25,B26,D1,D2,D8,

D9,D16,D17

Power for

DDR1 and

DDR2 DRAM

I/O voltage

(1.8/2.5 V)

—

LVDD

D24,D25,G23,H23,R23,

T23,W25,Y25,AA22,AC23

Power for local

bus (3.3 V)

—

LVDDA

W2,Y2

Power for

eTSEC2

(2.5 V, 3.3 V)

—

LVDDB

AC8,AC9,AE4,AE5

Power for

eTSEC1/

USB DR

(2.5 V, 3.3 V)

—

MVREF

C14,D14

Reference

voltage signal

for DDR

—

NVDD

G4,H4,L2,M2,AC16,AC17,

AD25,AD26,AE12,AE13,

AE20,AE21,AE24,AE25,

AE26,AF24,AF25

Standard I/O

voltage (3.3 V)

—

VDD

K11,K12,K13,K14,K15,

K16,L10,L17,M10,M17,

N10,N17,U12,U13,

Power for core

(1.0 V)

—

VDDC

F6,F10,F19,K6,K10,K17,

K21,P6,P10,P17,R10,R17,

T10,T17,U10,U11,U14,

U15,U16,U17,W6,W21,

AA6,AA10,AA14,AA19

Internal core

logic constant

power (1.0 V)

—

Table 63. MPC8313E TEPBGAII Pinout Listing (continued)

Signal

Package Pin Number

Pin Type

Power

Supply

Notes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC8313ECVRAFFB | 32-BIT, 333 MHz, MICROPROCESSOR, PBGA516 |

| MPC8313EVRAGDB | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA516 |

| MPC8313VRAGDB | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA516 |

| MPC8313VRAGDA | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA516 |

| MPC8313VRAFFB | 32-BIT, 333 MHz, MICROPROCESSOR, PBGA516 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8313ZQAGDC | 功能描述:微處理器 - MPU 8313 REV2.2 PB NO ENC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8313ZQGDD | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC? II Pro Processor Hardware Specifications |

| MPC8313ZQGDDA | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC? II Pro Processor Hardware Specifications |

| MPC8313ZQGDDB | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC? II Pro Processor Hardware Specifications |

| MPC8313ZQGDF | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC? II Pro Processor Hardware Specifications |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。