- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371014 > MC145162D (MOTOROLA INC) 60 MHz and 85 MHz Universal Programmable Dual PLL Frequency Synthesizers PDF資料下載

參數(shù)資料

| 型號: | MC145162D |

| 廠商: | MOTOROLA INC |

| 元件分類: | XO, clock |

| 英文描述: | 60 MHz and 85 MHz Universal Programmable Dual PLL Frequency Synthesizers |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 60 MHz, PDSO16 |

| 封裝: | SOG-16 |

| 文件頁數(shù): | 7/24頁 |

| 文件大小: | 223K |

| 代理商: | MC145162D |

MC145162

MC145162–1

MOTOROLA

7

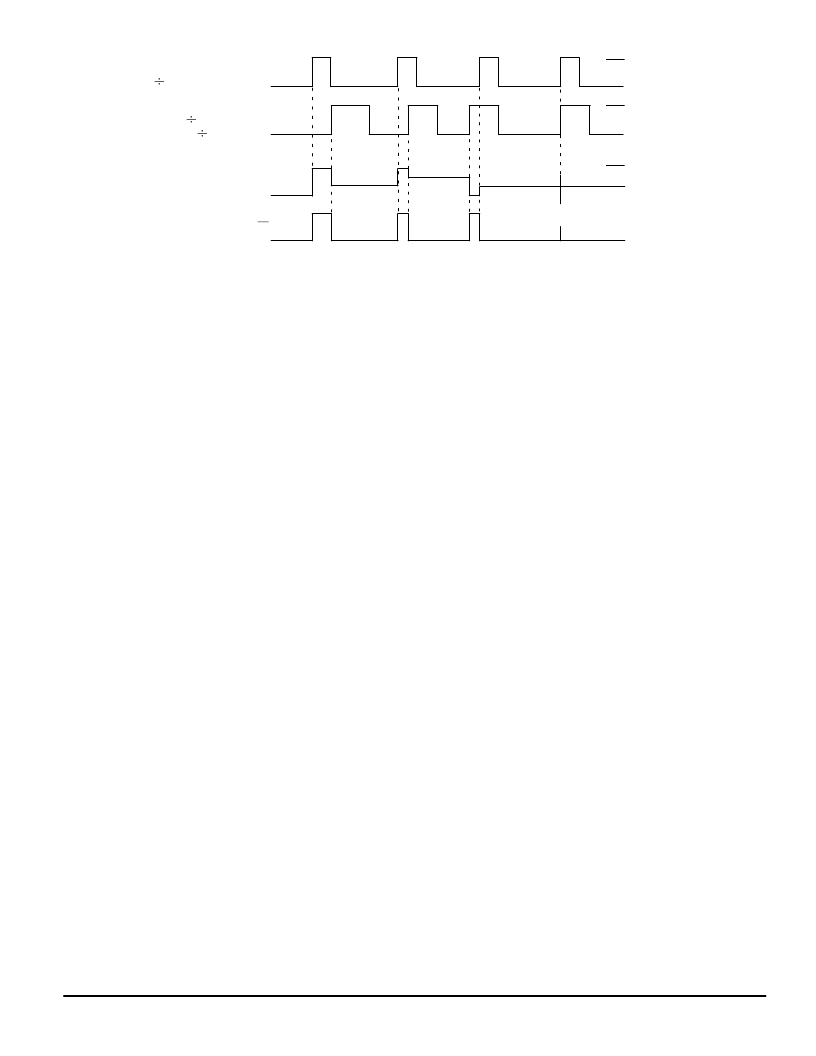

VH= High voltage level.

VL= Low voltage level.

*At this point, when both fR and fV are in phase, the output is forced to near mid supply.

NOTE: The TxPDout and RxPDout generate error pulses during out–of–lock conditions. When locked in phase and fre-

quency, the output is high impedance and the voltage at that pin is determined by the low–pass filter capacitor.

fR, REFERENCE

(OSCin

REFERENCE COUNTER)

fV, FEEDBACK

Tx COUNTER OR

fin–R

(fin–T

Rx COUNTER)

TxPDout

OR

RxPDout

VH

VL

VH

VH

VL

HIGH IMPEDANCE

*

Figure 7. Phase Detector/Lock Detector Output Waveforms

LD

MCU PROGRAMMING SCHEME

The MCU programming scheme is defined in two formats

controlled by the ENB input. If the enable signal is high during

the serial data transfer, control register/reference frequency

programming is selected. If the ENB is low, programming of

the transmit and receive counters is selected. During pro-

gramming of the transmit and receive counters, both ADin

and Din pins can input the data to the transmit and receive

counters. Both counters’ data is clocked into the PLL internal

shift register at the leading edge of the CLK signal. It is not

necessary to reprogram the reference frequency counter/

control register when using the enable signal to program the

transmit/receive channels.

In programming the control register/reference frequency

scheme, the most significant bit (MSB) of the programming

word identifies whether the input data is the control word or

the reference frequency data word. If the MSB is 1, the input

data is the control word (Figure 8). Also see Figure 8 and

Table 1 for control register and bit function. If the MSB is 0, the

input data is the reference frequency (Figure 9).

The reference frequency data word is a 32–bit word con-

taining the 12–bit reference frequency data, the 14–bit auxil-

iary reference frequency counter information, the reference

frequency selection plus, the auxiliary reference frequency

counter enable bit (Figure 9).

If the AUX REF ENB bit is high, the 14–bit auxiliary refer-

ence frequency counter provides an additional phase refer-

ence frequency output for the loops. If AUX REF ENB bit is

low, the auxiliary reference frequency counter is forced into

power–down mode for current saving. (Other power down

modes are also provided through the control register per

Table 2 and Figure 8.) At the falling edge of the ENB signal,

the data is stored in the registers.

There are two interfacing schemes for the universal chan-

nel mode: the three–pin and the four–pin interfacing

schemes. The three–pin interfacing scheme is suited for use

with the MCU SPI (serial peripheral interface) (Figure 10),

while the four–pin interfacing scheme is commonly used for

general I/O port connection (Figure 11).

For the three–pin interfacing scheme, the auxiliary data

select bit is set to 0. All 32 bits of data, which define both the

16–bit transmit counter and the 16–bit receive counter, latch

into the PLL internal register through the data in pins at the

leading edge of CLK. See Figures 12 and 13.

For the four–pin interfacing scheme, the auxiliary data

select bit is set to 1. In this scheme, the 16–bit transmit count-

er’s data enters into the ADin pin at the same time as the

16–bit receive counter’s data enters into the Din pin. This si-

multaneous entry of the transmit and receive counters

causes the programming period of the four–pin scheme to be

half that of the three–pin scheme (see Figures 14 and 15).

While programming Tx/Rx Channel Counter, the ENB pin

must be pulsed to provide falling edge to latch the shifted data

after the rising edge of the last clock. Maximum data transfer

rate is 500 kbps.

NOTE

10 ms should be allowed for initial start–up time

for the oscillator to allow all registers to clear and

enable programming of new register values.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC145162D1 | CONNECTOR ACCESSORY |

| MC145162P | 60 MHz and 85 MHz Universal Programmable Dual PLL Frequency Synthesizers |

| MC145162P1 | One Inverting, One Non-inverting AND Dual High-Speed MOSFET Drivers 8-SOIC |

| MC145165D | Low-Voltage 60 MHz Universal Programmable Dual PLL Frequency Synthesizer |

| MC145165P | Low-Voltage 60 MHz Universal Programmable Dual PLL Frequency Synthesizer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC145166DW | 制造商:Motorola Inc 功能描述:PLL FREQUENCY SYNTHESIZER, 60 MHz, PDSO16 |

| MC145167DW | 制造商:Motorola Inc 功能描述:PLL FREQUENCY SYNTHESIZER, 60 MHz, PDSO16 |

| MC145167P | 制造商:Motorola Inc 功能描述: 制造商:Motorola Inc 功能描述:Frequency Synthesizer, 16 Pin, Plastic, DIP |

| MC14516B | 制造商:Motorola Inc 功能描述: |

| MC14516BALD | 制造商:Motorola Inc 功能描述:Counter, Up/Down, 4 Bit Binary, 16 Pin, Ceramic, DIP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。