- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69021 > MB90F922NCPMC MICROCONTROLLER, PQFP120 PDF資料下載

參數(shù)資料

| 型號(hào): | MB90F922NCPMC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | MICROCONTROLLER, PQFP120 |

| 封裝: | 16 X 16 MM, 1.70 MM HEIGHT, 0.50 M PITCH, PLASTIC, LQFP-120 |

| 文件頁(yè)數(shù): | 44/72頁(yè) |

| 文件大小: | 2151K |

| 代理商: | MB90F922NCPMC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)當(dāng)前第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)

MB90920 Series

DS07-13750-3E

49

(Continued)

*1 : When the PLL multiplier is

× 1, × 2, × 3 or × 4 and the internal clock is 20 MHz < fCP ≤ 32 MHz, set

DIV2 bit

= “1”*4, CS2 bit = “1” in the PSCCR register.

[Example] When using a base oscillator frequency of 24 MHz at PLL

× 1 :

CKSCR register : CS1 bit

= “0”, CS0 bit = “0”

PSCCR register : DIV2 bit

= “1”*4 ,CS2 bit = “1”

[Example] When using a base oscillator frequency of 6 MHz at PLL

× 3 :

CKSCR register : CS1 bit

= “1”, CS0 bit = “0”

PSCCR register : DIV2 bit

= “1”*4 , CS2 bit = “1”

*2 : When the PLL multiplier is

× 2 or × 4 and the internal clock is 20 MHz < fCP ≤ 32 MHz, the following

settings are also supported.

PLL

× 2 : CKSCR register : CS1 bit = “0”, CS0 bit = “0”

PSCCR register : DIV2 bit

= “0”*4 ,CS2 bit = “0”

PLL

× 4 : CKSCR register : CS1 bit = “0”, CS0 bit = “1”

PSCCR register : DIV2 bit

= “0”*4 ,CS2 bit = “0”

*3 : When the PLL multiplier is set to

× 6 or × 8 set “DIV2 bit = “0”*4 CS2 bit = “1”

and “PLL2 bit

= 1” in the PSCCR register.

[Example] When using a base oscillator frequency of 4 MHz at PLL

× 6 :

CKSCR register : CS1 bit

= “1”, CS0 bit = “0”

PLLOS register : DIV2 bit

= “0”*4 ,CS2 bit = “1”

[Example] When using a base oscillator frequency of 3 MHz at PLL

× 8 :

CKSCR register : CS1 bit

= “1”, CS0 bit = “1”

PLLOS register : DIV2 bit

= “0”*4 ,CS2 bit = “1”

*4 : The DIV2 bit is assigned to bit 9 of the PSCCR register and the CS2 bit is assigned to bit 8 of the PSCCR

register. Both bits have a default value of “0”.

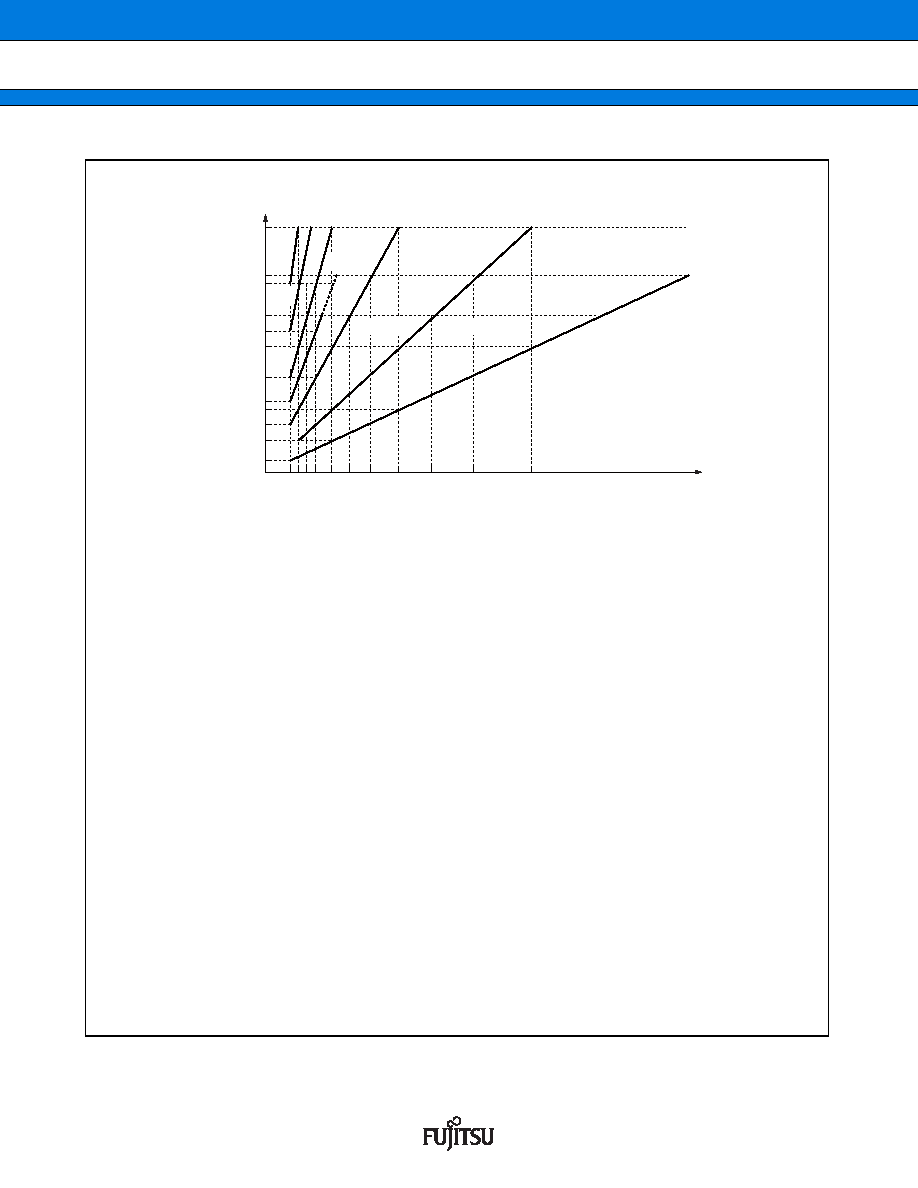

32

No multiplier

25

24

20

18

16

12

9

8

6

4

1.5

3 56 8 10 12.5 16

20

25

32

4

x 3*1

x 6*3

x 4

*1,*2

x 2*1,*2

x 1*1

x 8*3

Base oscillator frequency vs. Internal operating clock frequency

Base oscillator clock FCP (MHz)

Internal

clock

f

CP

(MHz)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB90F924NCPMC | MICROCONTROLLER, PQFP120 |

| MB90F946APF | MICROCONTROLLER, PQFP100 |

| MB90F947APF | MICROCONTROLLER, PQFP100 |

| MB90F949APF | MICROCONTROLLER, PQFP100 |

| MB90947APF | MICROCONTROLLER, PQFP100 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB90F947APFR-GS-SPE1 | 制造商:FUJITSU 功能描述: |

| MB90F962SPMCR-GE1 | 制造商:FUJITSU 功能描述:IC MCU 16BIT 16LX 48LQFP |

| MB90F962SPMCR-G-JNE1 | 制造商:FUJITSU 功能描述: |

| MB90V340A-102CR | 制造商:FUJITSU 功能描述: |

| MB-910 | 制造商:Circuit Test 功能描述:BREADBOARD WIRING KIT - 350 PCS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。