- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69021 > MB90F428GPF 16-BIT, FLASH, 16 MHz, MICROCONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | MB90F428GPF |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 16-BIT, FLASH, 16 MHz, MICROCONTROLLER, PQFP100 |

| 封裝: | PLASTIC, QFP-100 |

| 文件頁數(shù): | 81/99頁 |

| 文件大?。?/td> | 1714K |

| 代理商: | MB90F428GPF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁當前第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁

MB90420G/5G (A) Series

82

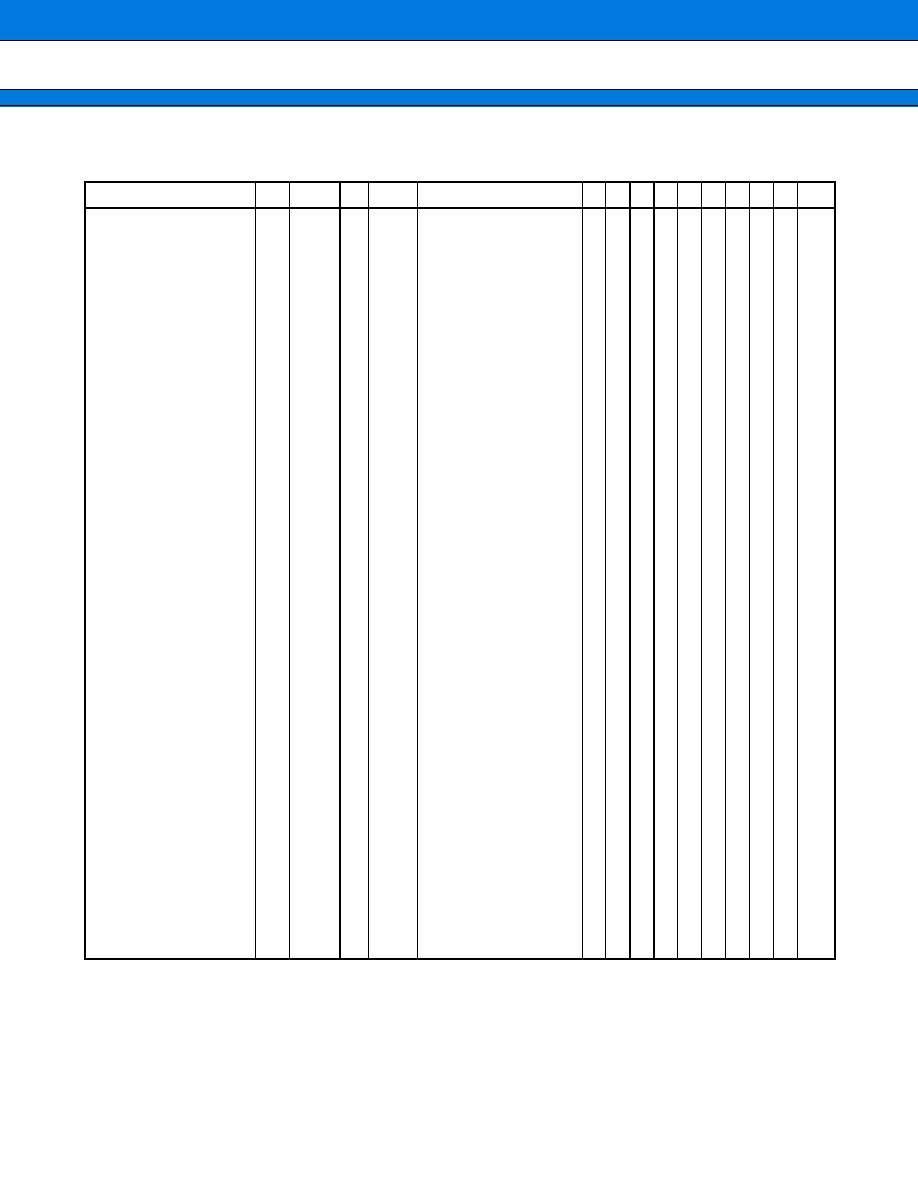

Table 7

Transfer Instructions (Byte) [41 Instructions]

Note : For an explanation of “(a)” to “(d)”, refer to Table 4, “Number of Execution Cycles for Each Type of Addressing,”

and Table 5, “Correction Values for Number of Cycles Used to Calculate Number of Actual Cycles.”

Mnemonic

#

~

RG

B

Operation

LH AH

I

S

T

N

Z

V

C

RMW

MOV

A, dir

MOV

A, addr16

MOV

A, Ri

MOV

A, ear

MOV

A, eam

MOV

A, io

MOV

A, #imm8

MOV

A, @A

MOV

A, @RLi+disp8

MOVN A, #imm4

MOVX

A, dir

MOVX

A, addr16

MOVX

A, Ri

MOVX

A, ear

MOVX

A, eam

MOVX

A, io

MOVX

A, #imm8

MOVX

A, @A

MOVX

A,@RWi+disp8

MOVX

A, @RLi+disp8

MOV

dir, A

MOV

addr16, A

MOV

Ri, A

MOV

ear, A

MOV

eam, A

MOV

io, A

MOV

@RLi+disp8, A

MOV

Ri, ear

MOV

Ri, eam

MOV

ear, Ri

MOV

eam, Ri

MOV

Ri, #imm8

MOV

io, #imm8

MOV

dir, #imm8

MOV

ear, #imm8

MOV

eam, #imm8

MOV

@AL, AH

/MOV

@A, T

XCH

A, ear

XCH

A, eam

XCH

Ri, ear

XCH

Ri, eam

2

3

1

2

2+

2

3

1

2

3

2

2+

2

3

2

3

1

2

2+

2

3

2

2+

2

2+

2

3

3+

2

2+

2

2+

3

4

2

3+ (a)

3

2

3

10

1

3

4

2

3+ (a)

3

2

3

5

10

3

4

2

3+ (a)

3

10

3

4+ (a)

4

5+ (a)

2

5

2

4+ (a)

3

4

5+ (a)

7

9+ (a)

0

1

0

2

0

1

0

1

2

0

1

0

2

1

2

1

0

1

0

2

0

4

2

(b)

0

(b)

0

(b)

0

(b)

0

(b)

0

(b)

0

(b)

0

(b)

0

(b)

0

(b)

0

(b)

0

2

× (b)

0

2

× (b)

byte (A)

← (dir)

byte (A)

← (addr16)

byte (A)

← (Ri)

byte (A)

← (ear)

byte (A)

← (eam)

byte (A)

← (io)

byte (A)

← imm8

byte (A)

← ((A))

byte (A)

← ((RLi)+disp8)

byte (A)

← imm4

byte (A)

← (dir)

byte (A)

← (addr16)

byte (A)

← (Ri)

byte (A)

← (ear)

byte (A)

← (eam)

byte (A)

← (io)

byte (A)

← imm8

byte (A)

← ((A))

byte (A)

← ((RWi)+disp8)

byte (A)

← ((RLi)+disp8)

byte (dir)

← (A)

byte (addr16)

← (A)

byte (Ri)

← (A)

byte (ear)

← (A)

byte (eam)

← (A)

byte (io)

← (A)

byte ((RLi) +disp8)

← (A)

byte (Ri)

← (ear)

byte (Ri)

← (eam)

byte (ear)

← (Ri)

byte (eam)

← (Ri)

byte (Ri)

← imm8

byte (io)

← imm8

byte (dir)

← imm8

byte (ear)

← imm8

byte (eam)

← imm8

byte ((A))

← (AH)

byte (A)

(ear)

byte (A)

(eam)

byte (Ri)

(ear)

byte (Ri)

(eam)

Z

X

–

Z

–

*

–

*

–

*

–

*

R

*

–

*

–

*

–

*

–

*

–

*

–

相關PDF資料 |

PDF描述 |

|---|---|

| MB90F474HPF | 16-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP100 |

| MB90474PF | 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP100 |

| MB90478PFV | 16-BIT, MROM, 20 MHz, MICROCONTROLLER, PQFP100 |

| MB90473PFV | 16-BIT, MROM, 20 MHz, MICROCONTROLLER, PQFP100 |

| MB90474PFV | 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP100 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MB90F438LSPFR-GE1 | 制造商:FUJITSU 功能描述: |

| MB90F438LSPMCR-GE1 | 制造商:FUJITSU 功能描述: |

| MB90F439PMCR-GE1 | 制造商:FUJITSU 功能描述: |

| MB90F439SPFR-GE1 | 制造商:FUJITSU 功能描述: |

| MB90F439SPFV-GE1 | 制造商:FUJITSU 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。