- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69018 > MB86605PMT SCSI BUS CONTROLLER, PQFP144 PDF資料下載

參數(shù)資料

| 型號(hào): | MB86605PMT |

| 元件分類: | 總線控制器 |

| 英文描述: | SCSI BUS CONTROLLER, PQFP144 |

| 封裝: | PLASTIC, LQFP-144 |

| 文件頁(yè)數(shù): | 2/64頁(yè) |

| 文件大小: | 275K |

| 代理商: | MB86605PMT |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

10

MB86605

(Continued)

3.

16-Bit Bus Mode – DMA Interface

(Continued)

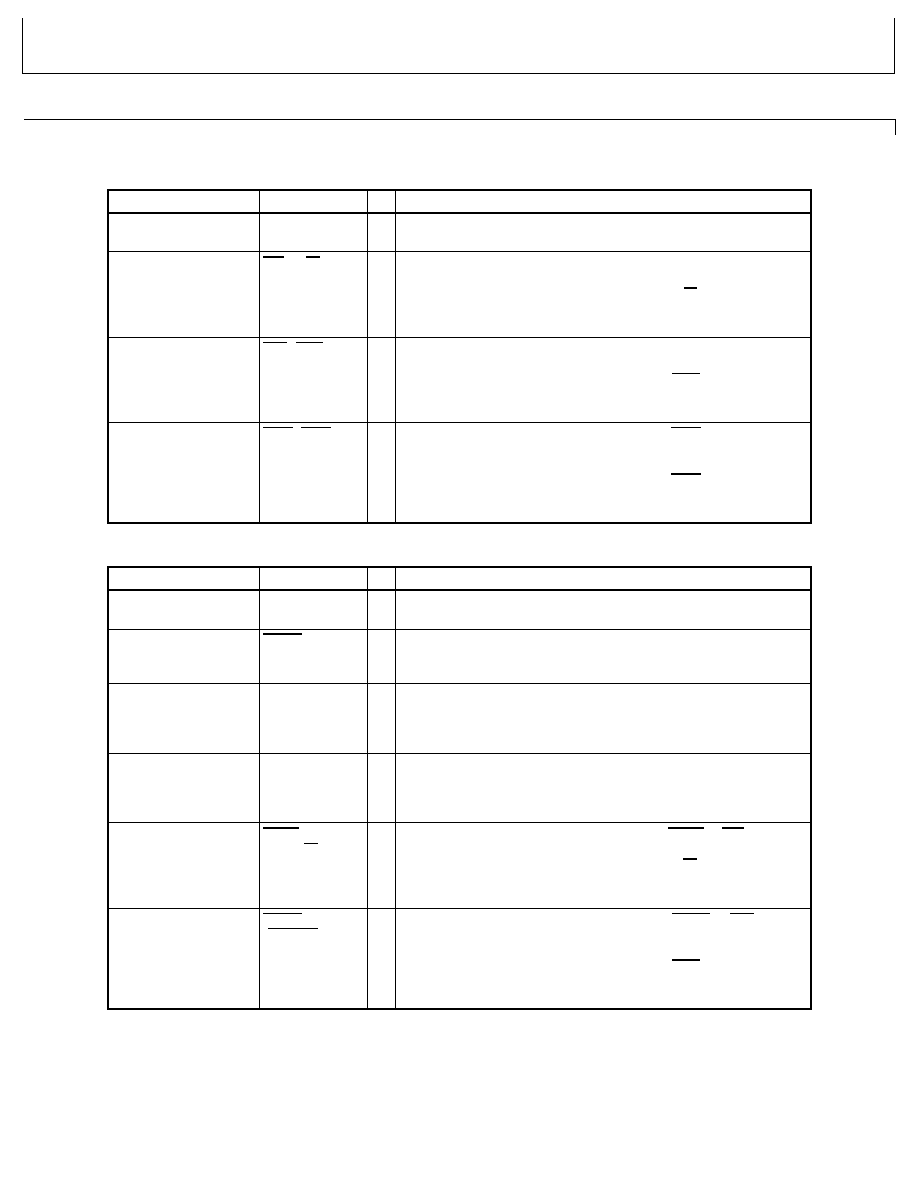

Pin no.

Pin name

I/O

Function

51, 52, 55 to 57

A4 to A0

IU These are used to input addresses for selecting the Internal

registers.

46

RD (R/W)

I

In 80-series mode: This is used to input the read strobe signal for

reading data from the SPC to the MPU.

In 68-series mode: This is used to input the R/W control signal for

reading and writing data from the MPU to the

SPC.

44

WR (LDS)

I

In 80-series mode: This is used to input the write strobe signal for

writing data from the MPU to the SPC.

In 68-series mode: This is used to input the LDS signal output by

the MPU when the lower byte of the data bus

is valid.

42

BHE (UDS)

I

In 80-series mode: This is used to input the BHE signal output by

the MPU when the upper byte of the data bus

is valid.

In 68-series mode: This is used to input the UDS signal output by

the MPU when the upper byte of the data bus

is valid.

Pin no.

Pin name

I/O

Function

130

DREQ

O This is used to output DMA transfer request signals to the DMAC.

DMA data transfer between the SPC and memory is requested.

129

DACK

I

This is used to input DMA-enabling signals from the DMAC.

When the DMA enabling signal is active, DMA reading and writing

are executed.

138, 139, 141 to 144, 1, 3

136

DMD15 to 8

UDMDP

I/O Upper byte and parity of DMA data bus

When CS1 input valid: The MPU data bus is directly connected.

When 80-series mode: The 2nd data is input/output.

When 68-series mode: The 1st data is input/output.

4, 5, 7, 9 to 11, 13, 14

15

DMD7 to 0

LDMDP

I/O Lower byte and parity of DMA data bus

When CS1 input valid: The MPU data bus is directly connected.

When 80-series mode: The 1st data is input/output.

When 68-series mode: The 2nd data is input/output.

135

IORD

(DMR/W)

I

In 80-series mode: This is used to input the IORD or RD signal for

outputting data from the SPC to the DMA bus.

In 68-series mode: This is used to input the R/W control signal for

outputting and inputting data from the DMAC

to the SPC.

133

IOWR

(DMLDS)

I

In 80-series mode: This is used to input the IOWR or WR signal

for inputting data from the DMA bus to the

SPC.

In 68-series mode: This is used to input the LDS signal output by

the DMAC when the lower byte of the DMA

data bus is valid.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB86606PMT | SCSI BUS CONTROLLER, PQFP144 |

| MB86612 | 2 CHANNEL(S), 98.304M bps, SERIAL COMM CONTROLLER, PQFP100 |

| MB86703PF | SPECIALTY MICROPROCESSOR CIRCUIT, PQFP80 |

| MB86831-66PFV-G | 32-BIT, 66 MHz, RISC PROCESSOR, PQFP176 |

| MB86832-80PFV-G | 32-BIT, 80 MHz, RISC PROCESSOR, PQFP176 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB86606A | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:FAST-20 SCSI Protocol Controller |

| MB86606APMT2 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:FAST-20 SCSI Protocol Controller |

| MB86612 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:IEEE 1394 Bus Controller (for MPEG, DVC) |

| MB86612PBT | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:IEEE 1394 Bus Controller (for MPEG, DVC) |

| MB86612PFV | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:IEEE 1394 Bus Controller (for MPEG, DVC) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。