- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377894 > MB86434 (Fujitsu Limited) 5V Single Power Supply Audio Interface Unit (AIU) PDF資料下載

參數(shù)資料

| 型號(hào): | MB86434 |

| 廠商: | Fujitsu Limited |

| 英文描述: | 5V Single Power Supply Audio Interface Unit (AIU) |

| 中文描述: | 5V單電源供電音頻接口單元(美亞) |

| 文件頁數(shù): | 3/38頁 |

| 文件大?。?/td> | 574K |

| 代理商: | MB86434 |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

MB86434

3

I

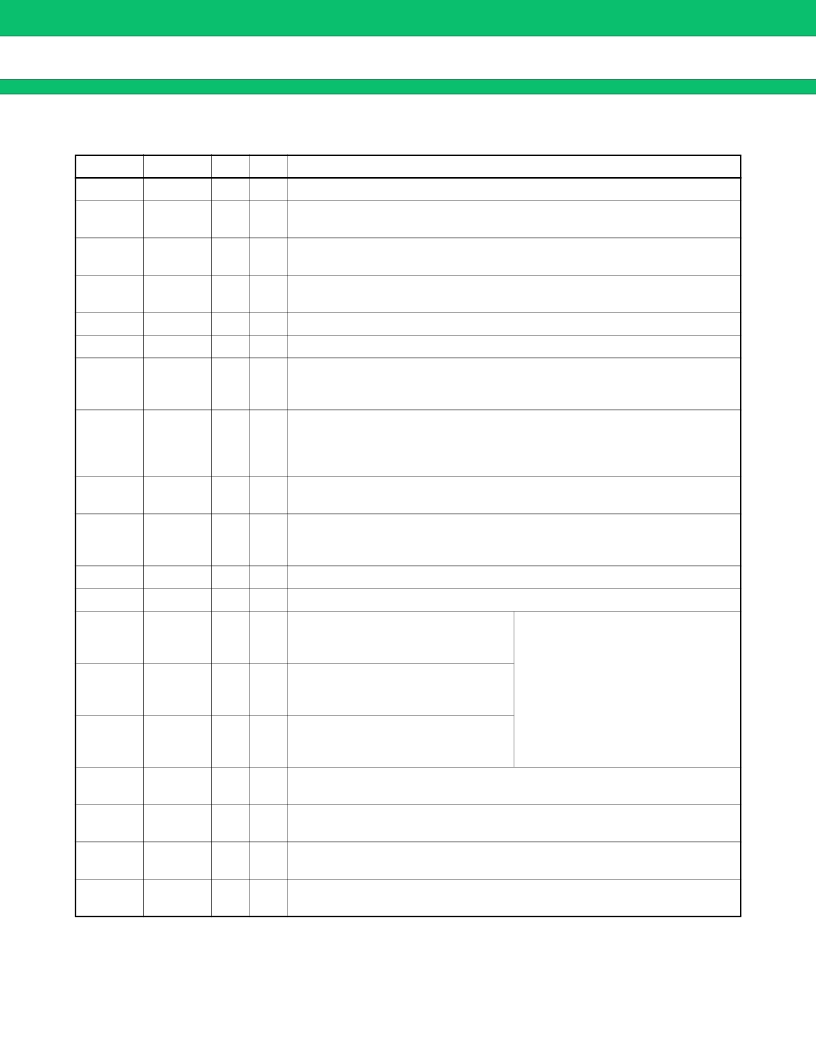

PIN DESCRIPTION

(Continued)

Pin No.

Symbol

I/O

A/D

Description

1

CAG

G

A

Analog ground pin for codec block. To be set to 0 V.

2

VRH

O

A

Bypass capacitor connector pin for the A/D D/A reference voltage generator

circuit. Place capacitor between VRH and CAG pins.

3

SGC

O

A

Bypass capacitor connector pin for the signal ground potential generator

circuit. Place capacitor between SGC and CAG pins.

4

VDDAC

P

A

Analog power supply pin for codec block. To be set within range 4.75 to

5.25 V.

5

N.C.

—

—

Not connected. To be left open.

6

N.C.

—

—

Not connected. To be left open.

7

SYNC

I

D

PCM codec send/receive synchronization signal input pin. Operating clock

frequencies 8 kHz. CMOS interface. Other frequencies may cause codec

block to power-down.

Send/receive PCM signal series bit rate setting input pin. Data rate for

μ

-law,

A-law modes may be set to any level in the range 64 k to 3.152 MHz, and for

linear in the range 256 k to 3.152 MHz. Constant H or L level signal will

cause part of codec block to power-down. CMOS interface.

8

CLK

I

D

9

DIN

I

D

PCM signal input pin. This signal is picked up internally at the fall of the CLK

signal. CMOS interface.

10

DOUT

O

D

PCM signal output pin. Data is output in sync with the rise of the CLK signal.

After data output, loses PLL synchronization, and at power-down this signal

is fixed at H level. CMOS interface.

11

VDD

P

D

Digital power supply pin. To be set within range 4.75 to 5.25 V.

12

DG

G

D

Digital ground pin. To be set to 0V.

13

PSC0

I

D

Power-down control signal input pin.

CMOS interface. Used with PSC1,2

pins for power-down settings.

PSC 2 1 0

0 0 0 Full power-down

1 0 0 V

REF

operating

—1 0 Tone operating

——1 All operations available

(—: value not determined)

14

PSC1

I

D

Power-down control signal input pin.

CMOS interface. Used with PSC0,2

pins for power-down settings.

15

PSC2

I

D

Power-down control signal input pin.

CMOS interface. Used with PSC0,1

pins for power-down settings.

16

SRD

I

D

9-bit serial data input pin. CMOS interface. Data is written at the rise of the

signal from this pin.

17

SRC

I

D

Clock input pin for 9-bit serial data writing. CMOS interface. Data is written

at the rise of this pin.

18

STB

I

D

Serial data latch strobe signal. Data is latched by the L level signal. CMOS

interface. On-chip pull-down resistance.

19

XPRST

I

D

Digital reset signal input pin. CMOS interface. L level: internal latch

initialization H level: normal operation

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB86434PF | 5V Single Power Supply Audio Interface Unit (AIU) |

| MB86435 | 3 V Single Power Supply Audio Interface Unit (AIU) |

| MB86435PFV | RES 360 OHM 1/16W 5% 0402 SMD |

| MB86602C | SCSI-II Protocol Controller (Differential)(SCSI-II 協(xié)議控制器) |

| MB86603 | Communication Control SCSI-II Protocol Controller(通信控制SCSI-II協(xié)議控制器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB86434PF | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:5V Single Power Supply Audio Interface Unit (AIU) |

| MB86435 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:3 V Single Power Supply Audio Interface Unit (AIU) |

| MB86435PFV | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:3 V Single Power Supply Audio Interface Unit (AIU) |

| MB86437 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:3 V Single Power Supply Audio Interface Unit (AIU) |

| MB86437PFV | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:3 V Single Power Supply Audio Interface Unit (AIU) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。