- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄11587 > MAX3420EETG+ (Maxim Integrated Products)IC USB PERIPH CONTROLLER 24TQFN PDF資料下載

參數(shù)資料

| 型號(hào): | MAX3420EETG+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 3/22頁 |

| 文件大小: | 0K |

| 描述: | IC USB PERIPH CONTROLLER 24TQFN |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 75 |

| 控制器類型: | USB 外設(shè)控制器 |

| 接口: | USB/串行 |

| 電源電壓: | 3 V ~ 3.6 V |

| 電流 - 電源: | 15mA |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 24-WFQFN 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 24-TQFN-EP(4x4) |

| 包裝: | 管件 |

| 產(chǎn)品目錄頁面: | 1407 (CN2011-ZH PDF) |

| 配用: | MAX3420EEVKIT-2+-ND - EVAL KIT FOR MAX3420E |

USB Peripheral Controller

with SPI Interface

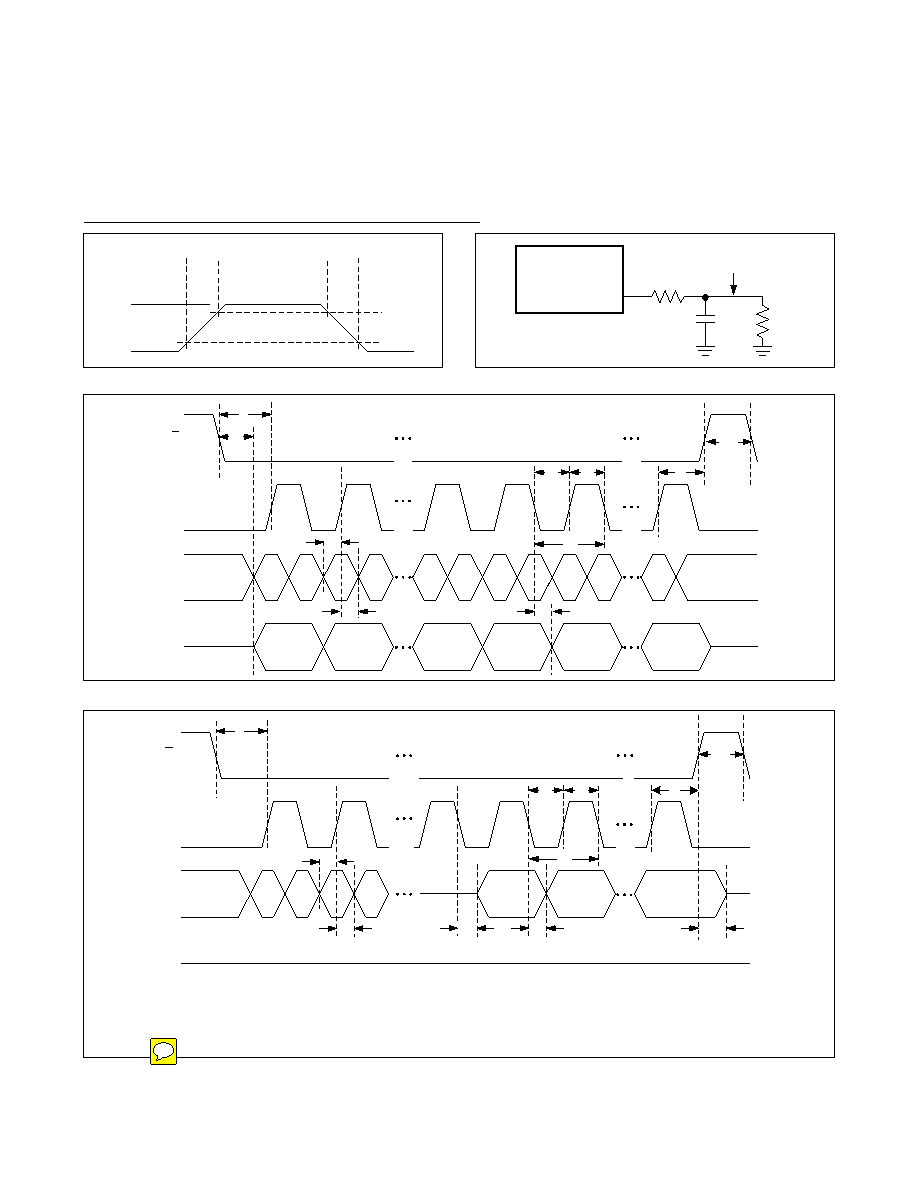

Test Circuits and Timing Diagrams

Figure 6. Rise and Fall Times

VOL

VOH

tRISE

tFALL

90%

10%

Figure 7. Load for D+/D- AC Measurements

MAX3420E

D+ OR D-

TEST

POINT

33

Ω

15k

Ω

CL

SCLK

SS

MOSI

MISO

tDS

tDH

tCL

tDO

tCH

tT

HIGH

IMPEDANCE

8

1

2

9

10

16

tL

tCSS

tCSW

tCP

HIGH

IMPEDANCE

Figure 9. SPI Bus Timing Diagram (Half-Duplex Mode, SPI Mode (0,0))

SCLK

MOSI

MISO

NOTES:

1) DURING THE FIRST 8 CLOCKS CYCLES, THE MOSI PIN IS HIGH IMPEDANCE AND THE SPI MASTER DRIVES DATA ONTO THE MOSI PIN. SETUP AND HOLD TIMES ARE THE SAME AS

FOR FULL-DUPLEX MODE.

2) FOR SPI WRITE CYCLES, THE MOSI PIN CONTINUES TO BE HIGH IMPEDANCE AND THE EXTERNAL MASTER CONTINUES TO DRIVE MOSI.

3) FOR SPI READ CYCLES, AFTER THE 8TH CLOCK-RISING EDGE, THE MAX3420E STARTS DRIVING THE MOSI PIN AFTER TIME tON. THE EXTERNAL MASTER MUST TURN

OFF ITS DRIVER TO THE MOSI PIN BEFORE tON TO AVOID CONTENTION. PROPAGATION DELAYS ARE THE SAME AS FOR THE MOSI PIN IN FULL-DUPLEX MODE.

tDS

tDH

tCL

tCH

tDI

tOFF

tT

SS

HI-Z

8

1

2

9

10

16

tL

tCSW

tON

tCP

HIGH IMPEDANCE

Figure 8. SPI Bus Timing Diagram (Full-Duplex Mode, SPI Mode (0,0))

MAX3420E

11

Maxim Integrated

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PIC12F629-E/SN | IC MCU CMOS 8BIT 1K FLASH 8-SOIC |

| PIC12LC508A-04I/MF | IC MCU OTP 512X12 LV 8DFN |

| PIC16F631-E/P | IC PIC MCU FLASH 1KX14 20DIP |

| PIC16C620A-04I/SO | IC MCU OTP 512X14 COMP 18SOIC |

| PIC12CE518-04I/SN | IC MCU OTP 512X12 W/EE 8SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX3420EETG+ | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI USB Peripheral Controller w/SPI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| MAX3420EETG+T | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI USB Peripheral Controller w/SPI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| MAX3420EETG-T | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| MAX3420EEVKIT | 制造商:Maxim Integrated Products 功能描述:MAX3420E EVAL KIT - Bulk |

| MAX3420EEVKIT-2+ | 功能描述:界面開發(fā)工具 MAX3420E Eval Kit RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評(píng)估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。