- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370998 > MAC7131VVF (Motorola, Inc.) MAC7100 Microcontroller Family Hardware Specifications PDF資料下載

參數(shù)資料

| 型號: | MAC7131VVF |

| 廠商: | Motorola, Inc. |

| 英文描述: | MAC7100 Microcontroller Family Hardware Specifications |

| 中文描述: | MAC7100微控制器系列硬件規(guī)格 |

| 文件頁數(shù): | 17/48頁 |

| 文件大小: | 1514K |

| 代理商: | MAC7131VVF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

17

MAC7100 Microcontroller Family Hardware Specifications

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

MOTOROLA

Electrical Characteristics

3.8.3

PLL Characteristics

3.8.4

Crystal Monitor Time-out

The time-out Table 19 shows the delay for the crystal monitor to trigger when the clock stops, either at the high

or at the low level. The corresponding clock period with an ideal 50% duty cycle is twice this time-out value.

3.8.5

Clock Quality Checker

The timing for the clock quality check is derived from the oscillator and the VCO frequency range in

Table 18. These numbers define the upper time limit for the individual check windows to complete.

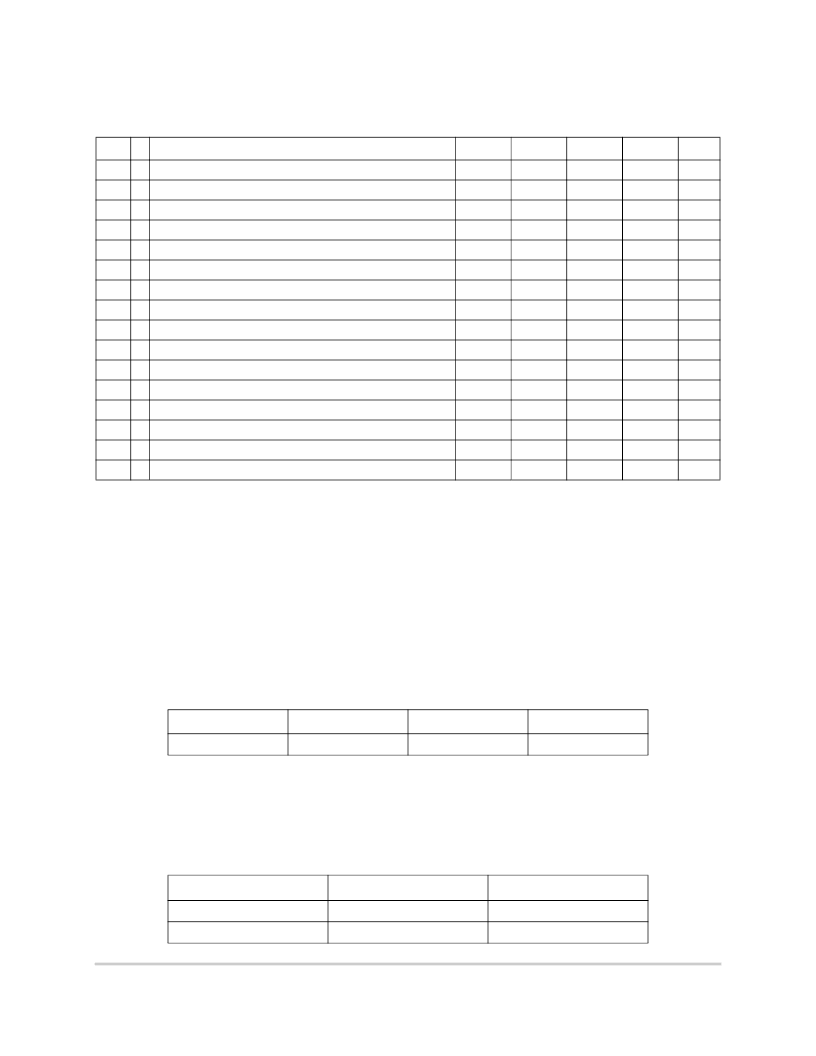

Table 18. PLL Characteristics

Num C

Rating

Symbol

Min

Typ

Max

Unit

J1

PLL reference frequency, crystal oscillator range

1

1

2

3

V

DD

PLL at 2.5 V.

Percentage deviation from target frequency

PLL stabilization delay is highly dependent on operational requirement and external component values (for

example, crystal and XFC filter component values). Notes 4 and 5 show component values for a typical

configurations. Appropriate XFC filter values should be chosen based on operational requirement of system.

f

REF

= 4 MHz, f

SYS

= 25 MHz (REFDV = 0x03, SYNR = 0x01), C

S

= 4.7 nF, C

P

= 470 pF, R

S

= 10 K

.

f

REF

= 4 MHz, f

SYS

= 8 MHz (REFDV = 0x00, SYNR = 0x01), C

S

= 33 nF, C

P

= 3.3 nF, R

S

= 2.7 K

.

f

REF

f

SCM

f

VCO

|

trk

|

|

Lock

|

|

unl

|

|

unt

|

t

stab

t

acq

t

al

|

i

ch

|

|

i

ch

|

K

1

f

1

j

1

j

2

0.5

—

16

MHz

J2

P Self Clock Mode frequency

1

—

5.5

MHz

J3

D VCO locking range

8

—

40

MHz

%

2

%

2

%

2

%

2

J4

D

Lock Detector transition from Acquisition to Tracking mode

3

—

4

J5

D Lock Detection

0

—

1.5

J6

D Un-Lock Detection

0.5

—

2.5

J7

D

Lock Detector transition from Tracking to Acquisition mode

C PLLON Total Stabilization delay (Auto Mode)

3

D PLLON Acquisition mode stabilization delay

3

D PLLON Tracking mode stabilization delay

3

6

—

8

J8

—

0.5

4

0.3

5

0.2

5

4

5

3

5

1

4

2

4

ms

J9

—

ms

J10

—

ms

μ

A

μ

A

J11

D Charge pump current acquisition mode

—

38.5

—

J12

D Charge pump current tracking mode

—

3.5

—

J13

D Jitter fit VCO loop gain parameter

—

–100

—

MHz/V

J14

D Jitter fit VCO loop frequency parameter

—

60

—

MHz

%

4

%

4

J15

C Jitter fit parameter 1

—

—

TBD

J16

C Jitter fit parameter 2

—

—

TBD

Table 19. Crystal Monitor Time-Outs

Min

Typ

Max

Unit

6

10

18.5

μ

s

Table 20. CRG Maximum Clock Quality Check Timings

Clock Check Windows

Value

Unit

Check Window

9.1 to 20.0

ms

Timeout Window

0.46 to 1.0

s

F

Freescale Semiconductor, Inc.

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAC7141VVF | MAC7100 Microcontroller Family Hardware Specifications |

| MAC97-8 | CONVERTER DC-DC 20W 24V/5V DUAL |

| MAC97-4 | TRIACs 0.8 AMPERE RMS 200 - 600 VOLTS |

| MAC97-6 | TRIACs 0.8 AMPERE RMS 200 - 600 VOLTS |

| MAC97A4 | TRIACs 0.8 AMPERE RMS 200 - 600 VOLTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAC7131VVF50 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Hardware Specifications |

| MAC7131VVF50R2 | 制造商:Freescale Semiconductor 功能描述: |

| MAC7131VVM50 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Hardware Specifications |

| MAC7132CAF50 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Hardware Specifications |

| MAC7132CAG50 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Hardware Specifications |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。