- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370991 > M66236FP (Mitsubishi Electric Corporation) STANDARD CLOCK GENERATOR PDF資料下載

參數(shù)資料

| 型號: | M66236FP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | STANDARD CLOCK GENERATOR |

| 中文描述: | 標(biāo)準(zhǔn)時鐘發(fā)生器 |

| 文件頁數(shù): | 2/5頁 |

| 文件大小: | 57K |

| 代理商: | M66236FP |

2

MITSUBISHI

DIGITAL ASSP

M66236FP

STANDARD CLOCK GENERATOR

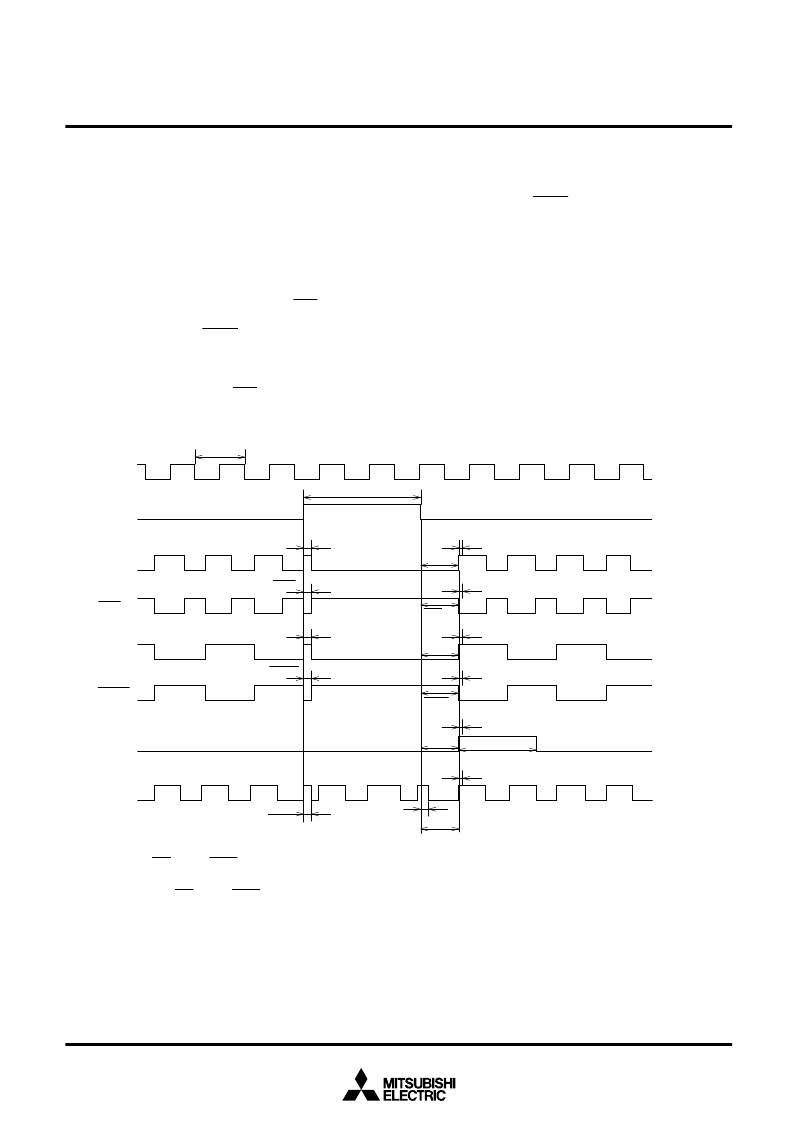

clock output from CKO is output. From 1/2 divider synchro-

nous clock output (CKO/2), 1/2 divider signal of sync clock

output from CKO is output. From 1/2 divider synchronous

clock inverted output (CKO/2), inverted signal of that output

from CKO/2 is output.

From one-shot pulse output (PULSE), one-shot pulse which

is almost equal to two cycles of clock input signal is output

after trigger input signal falls. From continuous clock output

(CNTCK), sync clock is output when trigger input signal is on

“L” level; when trigger input signal is on “H” level, clock input

signal, which is input to CLK IN, is output.

All these outputs but continuous clock output are suspended

when trigger input signal is on “H” level: Synchronous clock

output, 1/2 divider synchronous clock output and one-shot

pulse output stay on “L” level, and synchronous clock inverted

output and 1/2 divider synchronous clock inverted output stay

on “H” level.

CLK IN

1/f

IN

t

w(TR)

t

sp(CKO)

t

sp(CKO)

t

sp(CKO/2)

t

sp(CKO/2)

t

ss(CKO)

t

t

t

t

t

t

ss(CKO)

t

ss(CKO/2)

t

ss(CKO/2)

t

ss(PULSE)

t

w(PULSE)

t

t

CH

t

ss(CNTCK)

t

CL

TR

CKO

PULSE

CNTCK

CKO/2

CKO

CKO/2

3V

0V

0V

V

OH

V

OL

V

OH

V

OL

V

OH

V

OL

V

OH

V

OL

V

OH

V

OL

V

OH

V

OL

V

CC

Note 1: t

SS

(CKO, CKO, CKO/2, CKO/2 and PULSE) equals the sum of input clock “L” width and

α

. Value

α

refers to internal delay in M66236. Under envi-

ronment where temperature and V

CC

do not change, value

α

and t

ss

are kept constant. Dispersion of t

ss

under such conditions is defined as

t [syn-

chronizing precision (jitter)].

Note 2: Outputs (CKO, CKO, CKO/2, CKO/2 PULSE and CNTCK) are unknown until trigger input TR reaches “H” level for the first time after power-on.

FUNCTION

M66236 standard clock generator outputs clock input signal,

which is input to CLK IN, synchronously with optional trigger

signal, which is input to TR.

Sync clock output timing is determined by trigger input signal

fall edge. Time-lag between trigger input signal fall edge and

sync clock output equals the sum of clock input signal “L”

pulse width and M66236 internal delay. Variation in this lag

(

t) is

±

5ns, ensuring excellent synchronizing accuracy.

There are six types of outputs: synchronous clock output

(CKO), synchronous clock inverted output (CKO), 1/2 divider

synchronous clock output (CKO/2), 1/2 divider synchronous

clock inverted output (CKO/2), one-shot pulse output

(PULSE) and continuous clock output (CNTCK).

From synchronous clock output (CKO), sync clock of the

same frequency as clock input signal is output. From syn-

chronous clock inverted output (CKO), inverted signal of sync

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M66238FP | STANDARD CLOCK GENERATOR WITH PLL FREQUENCY SYNTHESIZER |

| M66240 | 4-CH 16-BIT PWM GENERATOR |

| M66240FP | 4-CH 16-BIT PWM GENERATOR |

| M66240P | 4-CH 16-BIT PWM GENERATOR |

| M66242FP | 4-CH 12-BIT PWM GENERATOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M66238FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:STANDARD CLOCK GENERATOR WITH PLL FREQUENCY SYNTHESIZER |

| M66238FP(#TF0T) | 制造商:Renesas Electronics Corporation 功能描述: |

| M66239FP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:High Speed Standard Clock Generator With Frequency Synthesizer |

| M66239FP(#RB0S) | 制造商:Renesas Electronics Corporation 功能描述: |

| M66240 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4-CH 16-BIT PWM GENERATOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。