- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370984 > M5M5V5636GP16 (Mitsubishi Electric Corporation) 18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM PDF資料下載

參數(shù)資料

| 型號(hào): | M5M5V5636GP16 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM |

| 中文描述: | 18874368位(524288 - Word的36位)網(wǎng)絡(luò)的SRAM |

| 文件頁(yè)數(shù): | 5/17頁(yè) |

| 文件大小: | 269K |

| 代理商: | M5M5V5636GP16 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)

MITSUBISHI LSIs

M5M5V5636GP –16

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

5

MITSUBISHI

ELECTRIC

Advanced Information

M5M5V5636GP REV.0.1

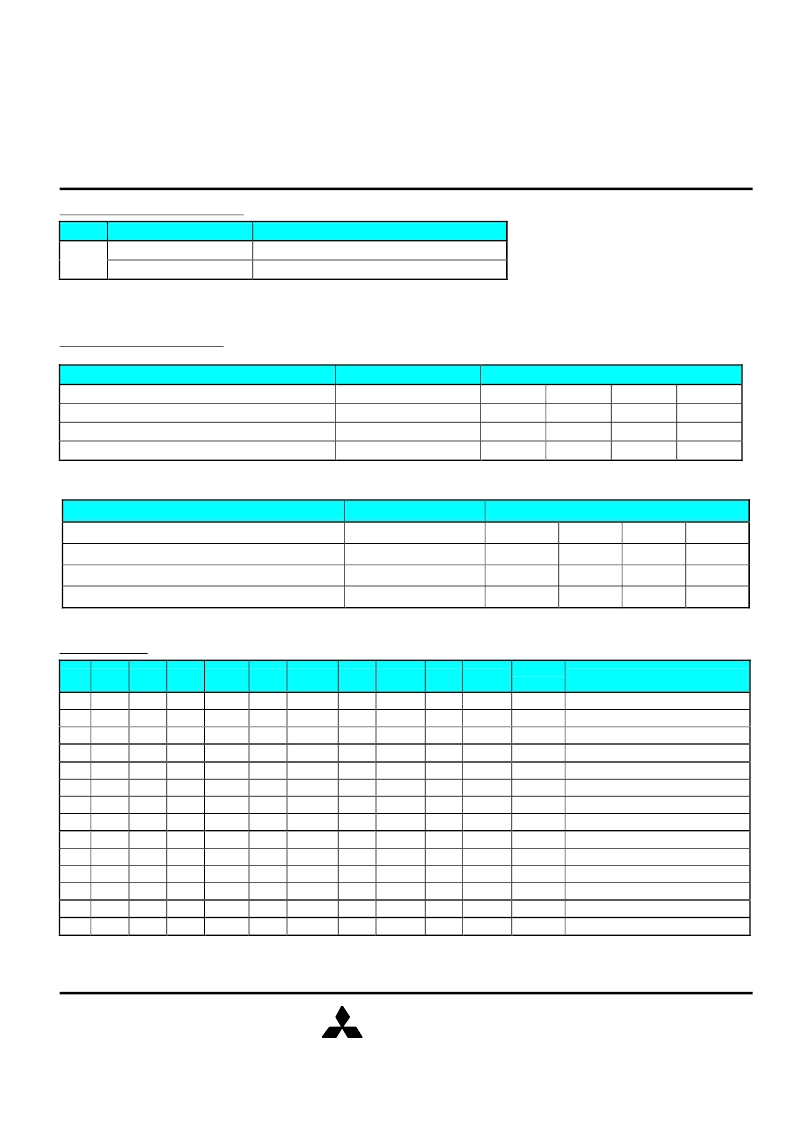

DC OPERATED TRUTH TABLE

Name

Input Status

HIGH or NC

LOW

Operation

Interleaved Burst Sequence

Linear Burst Sequence

LBO#

Note4. LBO# is DC operated pin.

Note5. NC means No Connection.

Note6. See BURST SEQUENCE TABLE about interleaved and Linear Burst Sequence.

BURST SEQUENCE TABLE

Interleaved Burst Sequence

(when LBO# = HIGH or NC)

Operation

First access, latch external address

Second access(first burst address)

Third access(second burst address)

Fourth access(third burst address)

A18~A2

A18~A2

latched A18~A2

latched A18~A2

latched A18~A2

A1,A0

0 , 0

0 , 1

1 , 0

1 , 1

0 , 1

0 , 0

1 , 1

1 , 0

1 , 0

1 , 1

0 , 0

0 , 1

1 , 1

1 , 0

0 , 1

0 , 0

Linear Burst Sequence

(when LBO# = LOW)

Operation

A18~A2

A1,A0

First access, latch external address

Second access(first burst address)

A18~A2

latched A18~A2

0 , 0

0 , 1

0 , 1

1 , 0

1 , 0

1 , 1

1 , 1

0 , 0

Third access(second burst address)

Fourth access(third burst address)

Note7. The burst sequence wraps around to its initial state upon completion.

latched A18~A2

latched A18~A2

1 , 0

1 , 1

1 , 1

0 , 0

0 , 0

0 , 1

0 , 1

1 , 0

TRUTH TABLE

E1#

E2

E3#

ZZ

ADV

W#

BWx#

G#

CKE#

CLK

DQ

Address

used

None

None

Operation

H

X

X

X

L

X

L

X

L

X

L

X

X

X

X

L

X

X

H

X

H

X

H

X

H

X

X

X

X

X

H

X

L

X

L

X

L

X

L

X

X

X

L

L

L

L

L

L

L

L

L

L

L

L

L

H

L

L

L

H

L

H

L

H

L

H

L

H

X

X

X

X

X

X

H

X

H

X

L

X

L

X

X

X

X

X

X

X

X

X

X

X

L

L

H

H

X

X

X

X

X

X

L

L

H

H

X

X

X

X

X

X

L

L

L

L

L

L

L

L

L

L

L

L

H

X

L->H

L->H

High-Z

High-Z

Deselect Cycle

Deselect Cycle

Deselect Cycle

Continue Deselect Cycle

Read Cycle, Begin Burst

Read Cycle, Continue Burst

NOP/Dummy Read, Begin Burst

Dummy Read, Continue Burst

Write Cycle, Begin Burst

Write Cycle, Continue Burst

NOP/Write Abort, Begin Burst

Write Abort, Continue Burst

Ignore Clock edge, Stall

Snooze Mode

L->H

High-Z

None

L->H

High-Z

None

L->H

L->H

L->H

Q

Q

External

Next

External

High-Z

L->H

High-Z

Next

L->H

D

External

L->H

L->H

L->H

D

Next

None

Next

High-Z

High-Z

L->H

-

Current

X

High-Z

None

Note8. X means "don't care". H means logic HIGH. L means logic LOW.

Note9. BWx#=H means all Synchronous Byte Write Enables (BWa#,BWb#,BWc#,BWd#) are HIGH. BWx#=L means one or more

Synchronous Byte Write Enables are LOW.

Note10. All inputs except G# and ZZ must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5M5W816TP-70HI | 8388608-BIT (524288-WORD BY 16-BIT) CMOS STATIC RAM |

| M5M5W816TP-85HI | 8388608-BIT (524288-WORD BY 16-BIT) CMOS STATIC RAM |

| M5M5W816WG-70HI | 8388608-BIT (524288-WORD BY 16-BIT) CMOS STATIC RAM |

| M5M5W816WG-85HI | 8388608-BIT (524288-WORD BY 16-BIT) CMOS STATIC RAM |

| M5M5W816WG-85H | 8388608-BIT (524288-WORD BY 16-BIT) CMOS STATIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M5M5V5636GP-16 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM |

| M5M5V5636GP-16_03 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM |

| M5M5V5636GP-16I | 制造商:Renesas Electronics Corporation 功能描述: |

| M5M5V5636GP-20 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM |

| M5M5V5636GP-22 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。