- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383304 > M5M4V64S40ATP-8 (Mitsubishi Electric Corporation) 64M (4-BANK x 1048576-WORD x 16-BIT) Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號: | M5M4V64S40ATP-8 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 64M (4-BANK x 1048576-WORD x 16-BIT) Synchronous DRAM |

| 中文描述: | 64M號(4銀行甲1048576字x 16位)同步DRAM |

| 文件頁數(shù): | 1/51頁 |

| 文件大小: | 1084K |

| 代理商: | M5M4V64S40ATP-8 |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

MITSUBISHI LSIs

MITSUBISHI ELECTRIC

SDRAM (Rev.1.3)

Mar'98

M5M4V64S40ATP-8A,-8L,-8, -10L, -10

64M (4-BANK x 1048576-WORD x 16-BIT) Synchronous DRAM

DESCRIPTION

The M5M4V64S40ATP is a 4-bank x 1048576-word x 16-bit

Synchronous DRAM, with LVTTL interface. All inputs and

outputs are referenced to the rising edge of CLK. The

M5M4V64S40ATP achieves very high speed data rate up to

125MHz, and is suitable for main memory or graphic memory

in computer systems.

FEATURES

- Single 3.3v±0.3v power supply

- Clock frequency 125MHz /100MHz

- Fully synchronous operation referenced to clock rising edge

- 4 bank operation controlled by BA0, BA1 (Bank Address)

- /CAS latency- 2/3 (programmable)

- Burst length- 1/2/4/8/Full Page (programmable)

- Burst type- sequential / interleave (programmable)

- Column access - random

- Burst Write / Single Write (programmable)

- Auto precharge / All bank precharge controlled by A10

- Auto refresh and Self refresh

- 4096 refresh cycles /64ms

- Column address A0-A7

- LVTTL Interface

- 400-mil, 54-pin Thin Small Outline Package (TSOP II) with

0.8mm lead pitch

Some of contents are subject to change without notice.

CLK

CKE

/CS

/RAS

/CAS

/WE

DQ0-15

DQML/U

A0-11

BA0,1

Vdd

VddQ

Vss

VssQ

: Master Clock

: Clock Enable

: Chip Select

: Row Address Strobe

: Column Address Strobe

: Write Enable

: Data I/O

: Output Disable/ Write Mask

: Address Input

: Bank Address

: Power Supply

: Power Supply for Output

: Ground

: Ground for Output

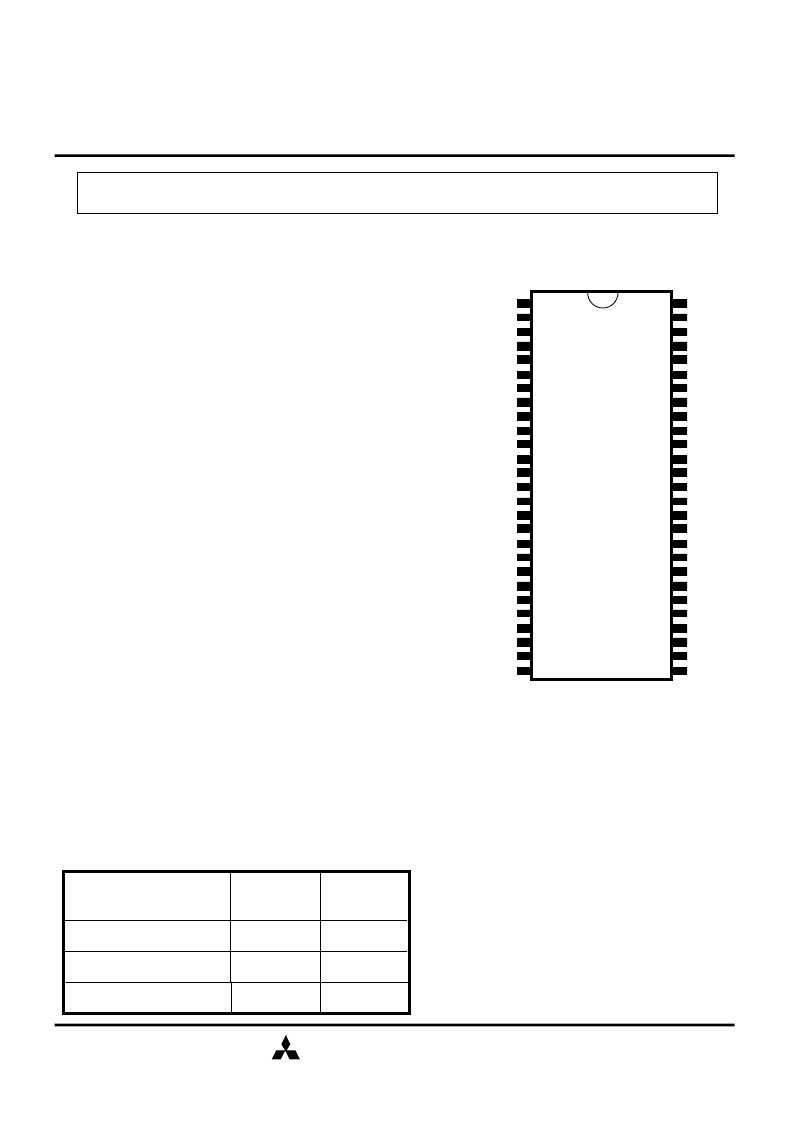

PIN CONFIGURATION

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

4

Vdd

DQ0

VddQ

DQ1

DQ2

VssQ

DQ3

DQ4

VddQ

DQ5

DQ6

VssQ

DQ7

Vdd

DQML

/WE

/CAS

/RAS

/CS

BA0(A13)

BA1(A12)

A10

A0

A1

Vss

DQ15

VssQ

DQ14

DQ13

VddQ

DQ12

DQ11

VssQ

DQ10

DQ9

VddQ

DQ8

Vss

NC (Vref)

DQMU

CLK

CKE

NC

A11

A9

A8

A7

A6

A5

A4

Vss

A2

A3

Vdd

Max.

Frequency

CLK Access

Time

M5M4V64S40ATP-8A

125MHz

6ns

1

M5M4V64S40ATP-10

100MHz

8ns

M5M4V64S40ATP-8

100MHz

6ns

相關PDF資料 |

PDF描述 |

|---|---|

| M5M4V64S40ATP-8A | 64M (4-BANK x 1048576-WORD x 16-BIT) Synchronous DRAM |

| M5M4V64S40ATP-8L | 64M (4-BANK x 1048576-WORD x 16-BIT) Synchronous DRAM |

| M5M51008CCP-55H | 1048576-BIT(131072-WORD BY 8-BIT)CMOS STATIC RAM |

| M5M51008CCP-55X | 1048576-BIT(131072-WORD BY 8-BIT)CMOS STATIC RAM |

| M5M51008CCP-70H | 1048576-BIT(131072-WORD BY 8-BIT)CMOS STATIC RAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M5M4V64S40ATP-8A | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 1048576-WORD x 16-BIT) Synchronous DRAM |

| M5M4V64S40ATP-8L | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 1048576-WORD x 16-BIT) Synchronous DRAM |

| M5M5 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEDIUM CURRENT SILICON RECTIFIERS |

| M5M51008AFP-10L | 制造商:Mitsubishi Electric 功能描述:Static RAM, 128Kx8, 32 Pin, Plastic, SOP |

| M5M51008AFP-10LL | 制造商:Mitsubishi Electric 功能描述:128K X 8 STANDARD SRAM, 100 ns, PDSO32 |

發(fā)布緊急采購,3分鐘左右您將得到回復。