- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359060 > M40Z300MH1 (意法半導(dǎo)體) NVRAM CONTROLLER for up to EIGHT LPSRAM PDF資料下載

參數(shù)資料

| 型號: | M40Z300MH1 |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | NVRAM CONTROLLER for up to EIGHT LPSRAM |

| 中文描述: | NVRAM中多達(dá)8個LPSRAM控制器 |

| 文件頁數(shù): | 4/16頁 |

| 文件大小: | 128K |

| 代理商: | M40Z300MH1 |

M40Z300, M40Z300W

4/16

DATA RETENTION LIFETIME CALCULATION

Most low power SRAMs on the market today can

be used with the M40Z300/W NVRAM Controller.

There are, however some criteria which should be

used in making the final choice of which SRAM to

use. The SRAM must be designed in a way where

the chip enable input disables all other inputs to

the SRAM. This allows inputs to the M40Z300/W

and SRAMs to be Don’t Care once V

CC

falls below

V

PFD

(min). The SRAM should also guarantee

data retention down to V

CC

= 2.0V. The chip en-

able access time must be sufficient to meet the

system needs with the chip enable propagation

delays included. If the SRAM includes a second

Chip Enable pin (E2), this pin should be tied to

V

OUT

.

If data retention lifetime is a critical parameter for

the system, it is important to review the data reten-

tion current specifications for the particular

SRAMs being evaluated. Most SRAMs specify a

data retention current at 3.0V. Manufacturers gen-

erally specify a typical condition for room temper-

ature along with a worst case condition (generally

at elevated temperatures). The system level re-

quirements will determine the choice of which val-

ue to use. The data retention current value of the

SRAMs can then be added to the I

CCDR

value of

the M40Z300/W to determine the total current re-

quirements for data retention. The available bat-

tery capacity for the SNAPHAT of your choice can

then be divided by this current to determine the

amount of data retention available (see Table 8).

CAUTION

: Take care to avoid inadvertent dis-

charge through V

OUT

and E1

CON

-E4

CON

after bat-

tery has been attached.

For a further more detailed review of lifetime cal-

culations, please see Application Note AN1012.

Table 3. Truth Table

Inputs

Outputs

E

B

A

E1

CON

E2

CON

E3

CON

E4

CON

H

X

X

H

H

H

H

L

L

L

L

H

H

H

L

L

H

H

L

H

H

L

H

L

H

H

L

H

L

H

H

H

H

H

L

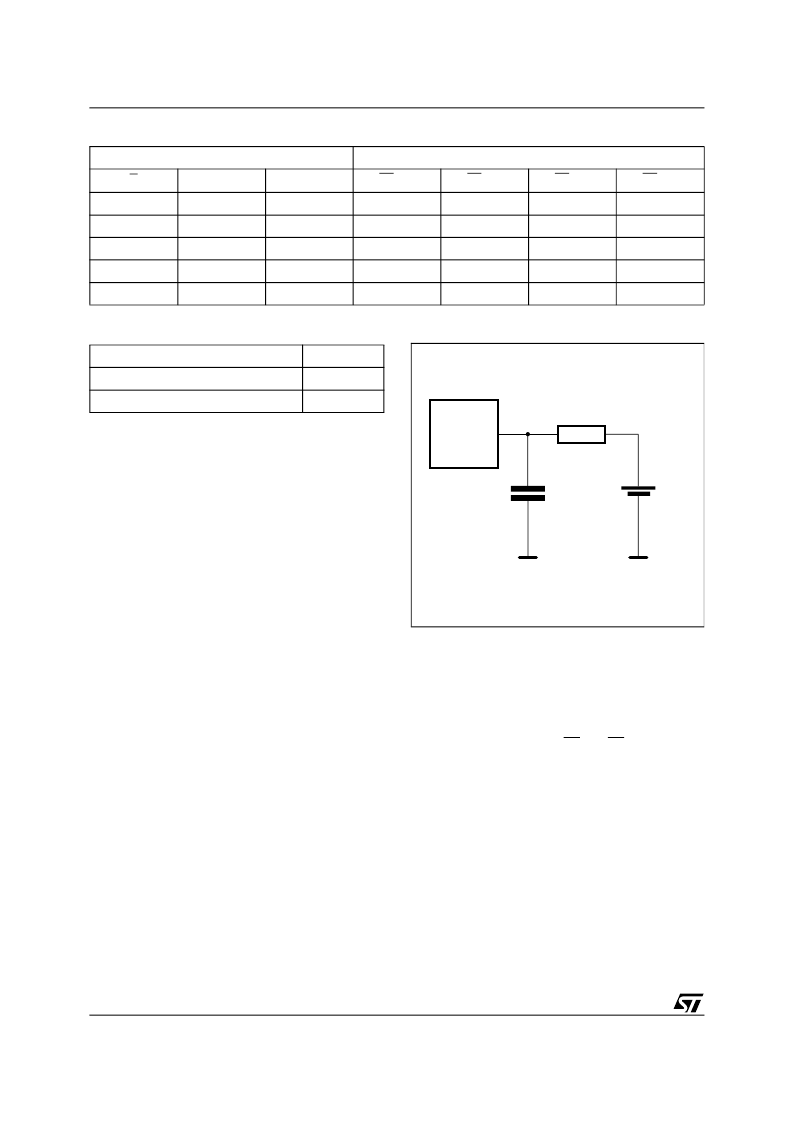

Figure 3. AC Testing Load Circuit

AI02393

CL = 50pF

CL includes JIG capacitance

333

DEVICE

UNDER

TEST

1.73V

Table 4. AC Measurement Conditions

Input Rise and Fall Times

≤

5ns

Input Pulse Voltages

0 to 3V

Input and Output Timing Ref. Voltages

1.5V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M40Z300MQ1 | CAP CER 4.7UF 4.0V 20% 0603 SMD |

| M40Z300MQ1TR | NVRAM CONTROLLER for up to EIGHT LPSRAM |

| M41ST85YSH | Shielded Multiconductor Cable; Number of Conductors:4; Conductor Size AWG:22; No. Strands x Strand Size:19 x 34; Jacket Material:Polyvinylchloride (PVC); Leaded Process Compatible:Yes; Temperature Max:105 C; Voltage Nom.:300V RoHS Compliant: Yes |

| M41ST85WMX6 | DIODE SCHOTTKY 25V 10A D2-PAK |

| M41ST85WSH | 5.0 OR 3.0V, 512 bit 64 x 8 SERIAL RTC and NVRAM SUPERVISOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M40Z300MH1E | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5V or 3V NVRAM supervisor for up to 8 LPSRAMs |

| M40Z300MH1F | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5V or 3V NVRAM supervisor for up to 8 LPSRAMs |

| M40Z300MH1TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5V or 3V NVRAM Supervisor for Up to 8 LPSRAMs |

| M40Z300MH6E | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5V or 3V NVRAM supervisor for up to 8 LPSRAMs |

| M40Z300MH6F | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5V or 3V NVRAM supervisor for up to 8 LPSRAMs |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。